主题中讨论的其他器件: TS3DV642、 TS3DV642-Q1

您好!

我将 TMUXHS4412用于 MIPI 设计、我在 S 参数中发现、P/N 端口之间存在8ps 的差异。

在数据表中、典型的传播延迟为4ps。 那么8ps 是最坏的情况吗? 它是否始终 P 端口长于 N 端口?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

我将 TMUXHS4412用于 MIPI 设计、我在 S 参数中发现、P/N 端口之间存在8ps 的差异。

在数据表中、典型的传播延迟为4ps。 那么8ps 是最坏的情况吗? 它是否始终 P 端口长于 N 端口?

您好、Xiaole:

我们的系统工程师将于下周(1/8)返回办公室。 我们可以在那时与他讨论这种行为。

同时、我想提几个问题、以便对您的仿真有更好的了解。

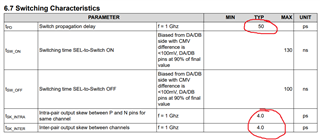

1. 4412数据表中的传播延迟通常在1GHz 时为50ps。 您提到、使用3个级联多路复用器、您可以看到30ps 的传播延迟是正确的吗?

2.在1GHz 时通道间的偏差通常为4ps,但是您看到3个级联4412的偏差为18ps,是否正确?

3.您需要哪种级别的偏斜? 如果18ps 过高、您在应用中合理的值有多大?

4.您是否在使用 Brian 为您的仿真发送的4412 s 参数文件?

此致!

谢恩

尊敬的 Shane:

我们更关心 PN 端口之间的偏差。 在您的数据表中、它是4p、但在 S 参数中、它是6ps。 这就是使用3个开关时我们看到更多偏斜的原因。

我们需要10ps 内的总偏斜、包括开关和引线。 我们可以平衡板上的偏斜与不同的布线长度。 但不确定应该使用哪个偏斜数作为偏移来保持偏斜。

我们现在的运行频率是1.75GHz、并使用 Brian 的 s 参数。

您好、Xiaole:

查看系统后、 数据表中的偏斜(4P)是多个器件上所有4个通道的平均值、而 S 参数偏斜(6ps)尤其在一个器件上的一个或两个通道之后建模。 这可以解释数据表和 S 参数之间存在2PS 差异的原因。

我们怀疑封装上引脚之间的长度差异可能会导致通道1上的 P 路径比 N 路径上的延迟稍大。 由于输入/输出引脚之间的长度发生变化、这在所有通道上并不一致。 此处是多路复用器、圈出了输入/输出引脚、有助于将长度变化可视化。

当您考虑所有引脚都连接到 封装内的 IC 芯片时、从 D0P 到 DA0P 的长度可能比从 D0N 到 DA0N 的长度更长。 当您向下移动时、可能会出现相反的情况。 例如、DB3N 可能略长于 DB3P、因为 DB3N 从封装内的 IC 芯片延伸得更远。

此致!

谢恩