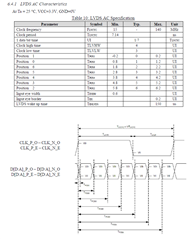

在 DOC slld009的第22页。 输入电压阈值用于接收器、只有 Vit 超过100mV、接收器将获得信号、如果低至100mV、它将忽略该信号、作为通信电压。

https://www.ti.com/lit/pdf/slld009

差分输入电压阈值

传输线路的输入信号是驱动器输出电压;差分接收器必须检测

版本。 为接收器考虑的第一个参数是差分输入电压阈值 VIT、因为它

定义了改变接收器输出状态所需的电压。 指定的最大和最小 VIT

建立 VIT 限制、高于或低于这些限制的差分电压可确保接收器指示

其输出端具有有效的逻辑状态。

EIA/TIA-644-A 标准规定了所有标准下的最大为100mV、最小 VIT 为–100mV

整个 CMTI 工作条件和输入共模电压范围内的变化情况。 驱动器差分电压为150伏时、

247mV 的输出电压、这将提供147mV 的最差情况差分噪声裕量。 尽管这可能

看起来值很小、平衡良好的差分传输系统中的干扰几乎会

无差分噪声。

除了 TIA/EIA-899驱动器的最低输出电压外、符合标准的接收器必须具有

对于1类接收器、最大为50mV、最小 VIT 为–50mV、最小差分为400mV

噪声容限。 TIA/EIA-899还指定了2类接收器、具有150mV 的最大 VIT 和最小值

50mV。 2类接收器的偏移 VIT 允许0V 差值成为有效的总线状态、并适用于

有线逻辑信号传输或失效防护措施。 图2–3显示了输入电压的图形化汇总

阈值

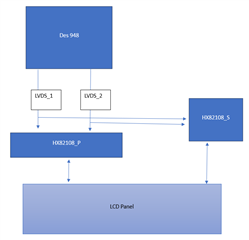

在948之类的转移装置处、它标记为 P/N Cross 作为测试点?

在948数据表第20页

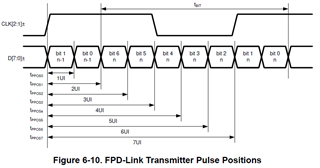

图6-10. FPD-Link 发送器脉冲位置