使用 THVD8000收发器、 观察到的总线争用行为应该是什么? 对于显性和隐性位冲突的所有组合、观察结果是否都是确定的?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、Rade、

遗憾的是、对于一个看似简单的问题、它实际上是一个相当复杂的答案。

最终、输入阈值决定了"R"引脚上的输出-无论总线状态如何、差分输入电压都是最终的决定因素。

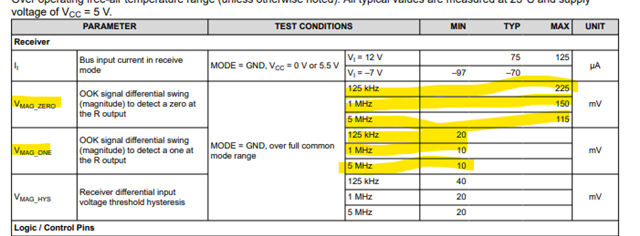

考虑到这些数字(这些数字会随所选的调制频率而变化)、接下来的分析就可以开始了。

通常、在显性状态下、您会观察驱动器的5至10欧姆输出阻抗。

如果多个驱动器处于显性状态、并且至少有一个驱动器异相、则 总线将短路-在这种情况下、由于差分电压应接近0伏、总线将读取到逻辑高电平。 然而、这可能由于以下事实而变得复杂:对于彼此同相的信号、可能让总线读取逻辑低电平-通常情况下、此时信号会变得混乱。 对于快速芯片(即器件异相但不是完全180度),内部带通滤波器可能会过滤掉信号,但仍被读取为逻辑高电平。 因此、多个显性驱动器尝试访问总线将导致不良数据-但根据信号异相的程度、将确定总线是否"短路"。 如果总线短路、它将在输出上变为高电平。

现在隐性状态没有被强烈驱动——我们估计它(数据表中没有直接指明)约为60欧姆,设定点为2.5V (它实际上是 VCC 的一半——但最终 VCC = 5V 是最佳性能的首选)。 如果多个器件尝试在隐性状态下访问总线、处于接收模式的器件将接收到逻辑高电平信号(VOD ~ 0V) 但是,如果处于显性模式的驱动器试图访问总线,由于显性模式驱动器上的输出阻抗较低,它很可能会覆盖总线上的隐性状态。 总线上处于隐性模式的器件越多、驱动器对其进行覆盖的可能性就越小。 然而、最大的问题是、这个分析只适用于短总线应用-总线越长、就越有可能发生总线争用导致 VOD = 0V -但这并不能保证。

总的来说、您可以将这些情况视为:

1.多次显性传输-取决于所有信号的相位、但会导致总线"短路"并在有源接收器输出端显示高电平-最终、A 相位差信号越多、它不被读取为逻辑低电平信号的可能性就越大。 至少、如果发生短路、数据信号很可能会无法通过固件中执行的任何数据完整性检查。

2.多次隐性传输-将被差分接收器读作逻辑高电平

3.混合显性(1)和隐性传输–高度依赖于调制频率、布线、总线距离和负载。 在短总线设置中、显性信号将覆盖隐性状态-不过驱动器的隐性状态阻抗远低于 RS -485器件的标准阻抗-因此预期的衰减量更高。 这可能会导致显性状态不会覆盖隐性状态。 这主要是在显示处于最后一个接收器的 VOD 几乎无法满足 VMAG_ZERO 阈值(裕量不大)的应用中的问题。 可能会产生隐性+显性混合导致显性位下降得太低、而接收器读取到逻辑高电平的情况。

通常-在某些情况下、显性状态将覆盖隐性状态、但根据实际的总线设置、它可能会导致这一情况不一定为真-但多个试图同时访问总线的显性状态将导致总线短路或 输出数据流中的数据损坏、应能够被固件捕获。 考虑该器件的总线争用时、最好的办法是使用可检测不良信息帧的良好固件、因为硬件可以处理总线争用而不会损坏、但由于其隐性输出状态、其确定性不如标准 RS -485的确定性差。

如果您有任何其他问题、敬请告知!

此致!

帕克·道德森