HII TI 大师级的

我已经使用 TFP401PZP TMDS DVI 接收器/解串器(来自 Mouser Electronics)设计了我自己的显示驱动程序板、该解串器连接到分辨率为800x480的24位并行 RGB 7英寸电容式触摸显示。

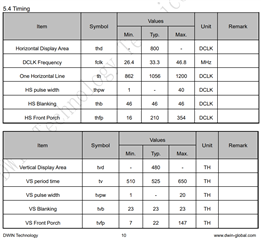

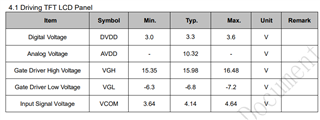

显示数据表: https://www.dwin-global.com/uploads/LCD-DATASHEET-LN80480T070IB3098.pdf

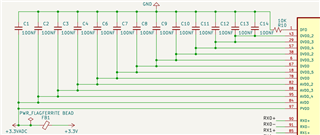

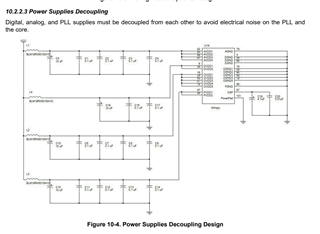

所有细分市场的配电都做到了完美。 驱动器板采用2层 PCB 设计(背层仅专用于接地层)。

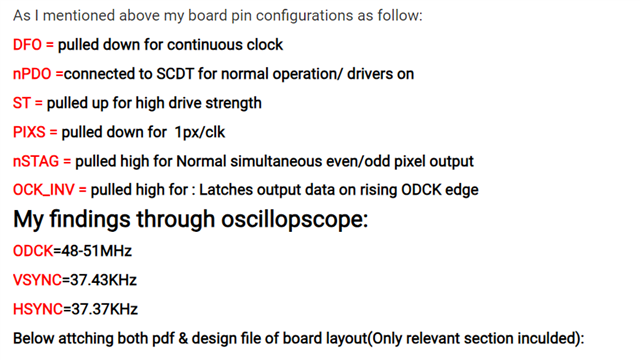

根据 IC 数据表、我还以以下方式设置了引脚参数:

DFO = L

nPDO = H,通过0 Ω 连接到引脚8。

ST =高

Pixs = L,1px/clk

nSTAG = H

OK_INV = H

还将 EDID 设置为具有800x480分辨率的外部 EEPROM。

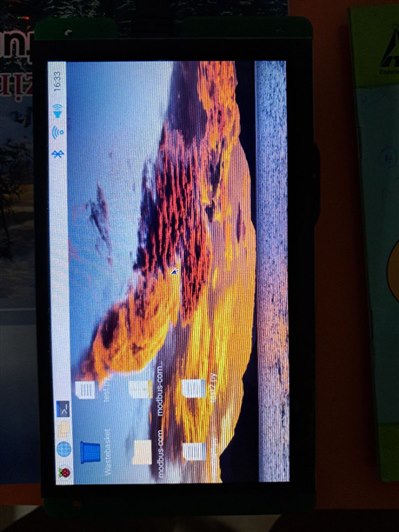

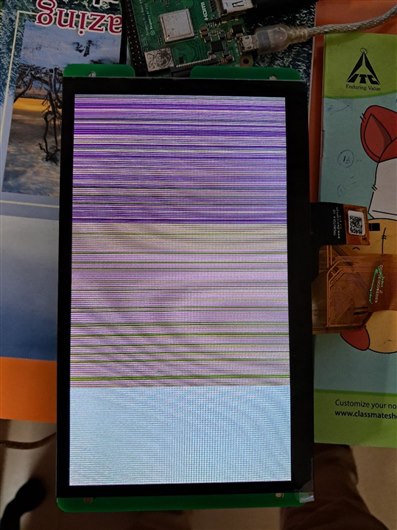

但在输出时,我得到失真的视频(鬼屏幕/像素不匹配)绿色水平线条。 我还分享了视频输出屏幕和电路板及原理图。

链接:https://imgur.com/a/pT2oVtv

原理图如下所示:

e2e.ti.com/.../4863.DISPLAY.pdf

此不良视频输出的原因可能是什么、或者通常有什么问题?

我们将非常感谢您提供任何帮助。

谢谢、此致

阿里吉特