先生,

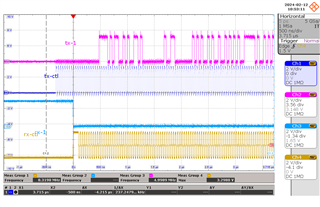

我尝试进行通信两个 DP83822、但我在 Rx 引脚上始终接收到0x5。

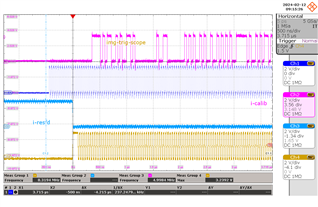

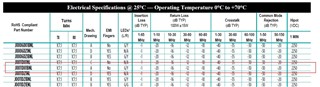

我尝试用 MII 进行回送、结果正常、我收到了我 发送的帧(第一张图片)。

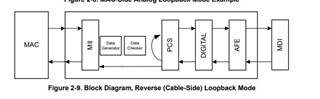

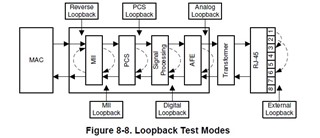

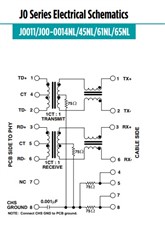

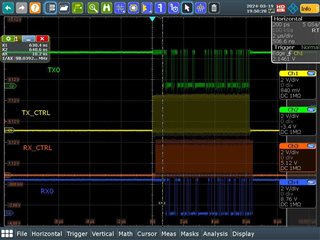

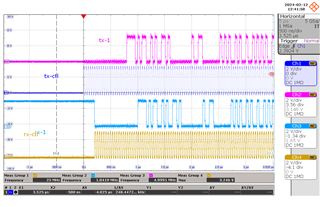

但当我尝试使用 Pcs 环回时、Rx 引脚始终处于0x5值上、Tx_ER 在两个前半字节上为1。 (第二张图片)。 当我从其他 PHY 接收数据时、我具有相同的行为。

我认为电脑不能编码或解码,但我不知道为什么。

我设置此配置:

Disable_all_IRQ; //Correct Strap pin config //Disable FX, FPGA pin must sink current so strap not read correctly ClearBit(this, CR2, FX_Enable_bit); SetBit(this,BMCR,Speed_Selection_bit); SetBit(this,BMCR,Autoneg_Enable_bit); SetBit(this,BMCR,DuplexMode_bit); SetBit(this, ANAR, Tx_100b_full_bit); //advertise 100Mbps SetBit(this, ANAR, Tx_100b_half_bit); //advertise 100Mbps ClearBit(this, ANAR, TXe_10b_full_bit); ClearBit(this, ANAR, TXe_10b_half_bit); //active rgmii ClearBit(this, RCSR, RMII_Mode_bit); SetBit(this, RCSR, RGMII_Mode_bit); ClearBit(this, RCSR, RMII_Clock_bit); ClearBit(this, LEDCR, LED_0_Polarity_bit); //Enable auto mdi SetBit(this, PHYCR, Enable_AutoMDI_bit); ClearBit(this, PHYCR, Led_CFG_bit); ClearBit(this, MLEDCR, MLED_Pol_bit); SetBit(this, IOCTRL1, 0); //TODO refaire globale ClearBit(this,IOCTRL1,1); ClearBit(this,IOCTRL1,2); ClearBit(this, EEECFG3,EEE_capabilites_bit); ClearBit(this, EEE_ADV, Adv_EEE_100bps_bit); //clear energyefficient ClearBit(this,RXCFG,WoL_Enbale_bit); //disable WoL

这里是 MII 环回的屏幕截图

在这里使用 pcs 环回

我使用 DP83xx811执行相同的操作、它运行正常。

我必须错过一些东西、并尝试许多配置。

您能给我一些建议尝试吗?

谢谢你。