大家好、团队

关于 DP83867IRRGZT 的 RGMII 信号、它们包括 TX_CLK、TX_D[3:0]、RX_CLK、RX_D[3:0]、 TX_CTRL、RX_CTRL、MDC、MDIO、INT_PWDN、 重置_N。 PCB 布局中的信号间隔要求是什么? 如果根据读取和写入进行分组、则为 MDC、MDIO、INT_PWDN、RESET_N 能否将它们分配到读取组或写入组? 还是一个单独的组? 非常感谢。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

大家好、团队

关于 DP83867IRRGZT 的 RGMII 信号、它们包括 TX_CLK、TX_D[3:0]、RX_CLK、RX_D[3:0]、 TX_CTRL、RX_CTRL、MDC、MDIO、INT_PWDN、 重置_N。 PCB 布局中的信号间隔要求是什么? 如果根据读取和写入进行分组、则为 MDC、MDIO、INT_PWDN、RESET_N 能否将它们分配到读取组或写入组? 还是一个单独的组? 非常感谢。

您好、 Gerome。

感谢您的答复。

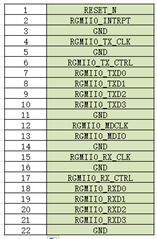

如下图所示、信号计划传输到连接器、连接器的引脚间距为0.5mm。 由于没有足够的引脚、因此我想删除一些 GND 引脚。 我认为仍然有必要保留时钟信号两侧的 GND 引脚。 能否移除图中引脚11的 GND? 是否需要将 GND 引脚与读取和写入信号隔离? 你有什么好的意见吗? 您能帮助我优化这种信号布局吗? 5W 线路间距良好、但难以实现。 谢谢。