主题中讨论的其他器件: TMDS64EVM、 DP83867ERGZ-S-EVM、 DP83869HM、DP83869EVM、 DP83869

大家好、团队成员:

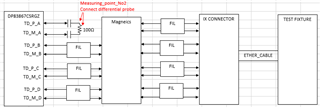

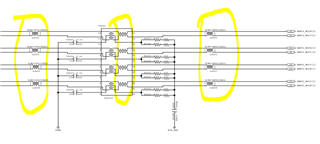

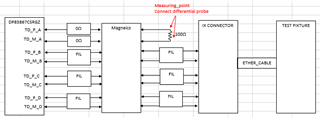

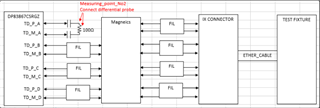

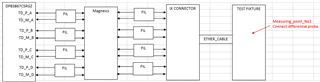

我们在开发板上使用了 DP83867CS、

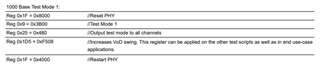

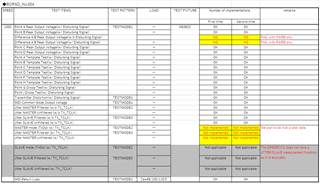

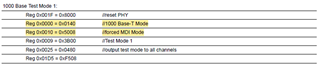

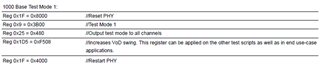

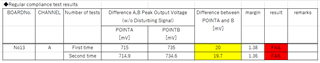

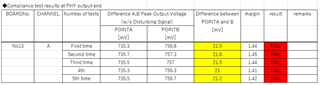

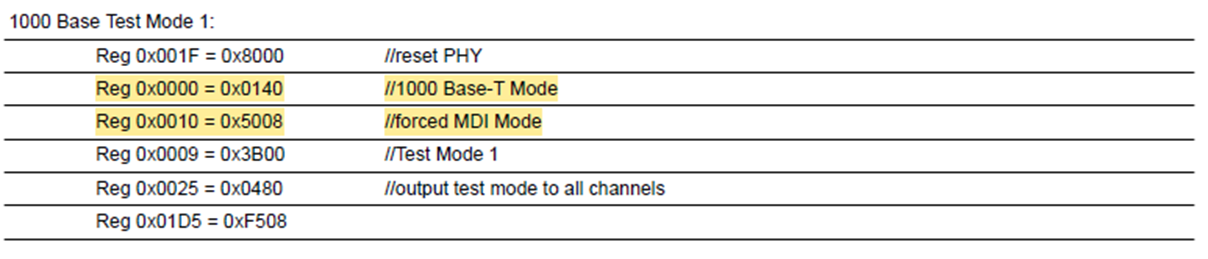

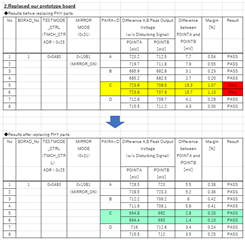

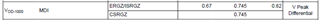

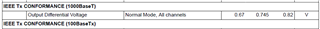

1000Base-T 合规性测试期间出现问题。

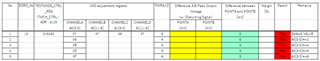

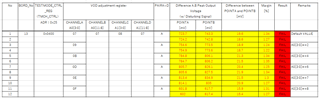

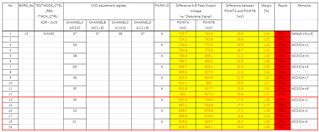

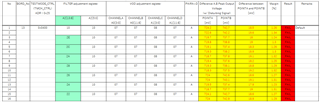

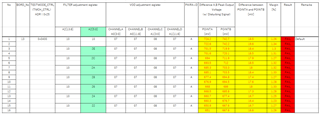

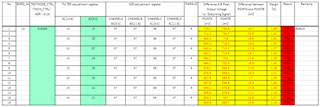

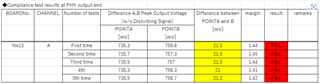

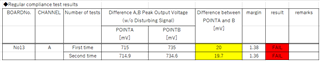

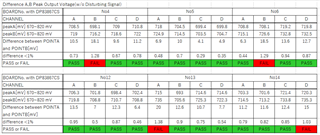

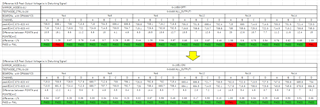

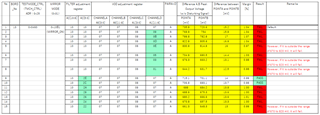

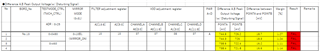

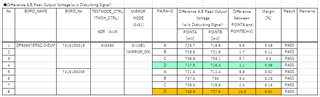

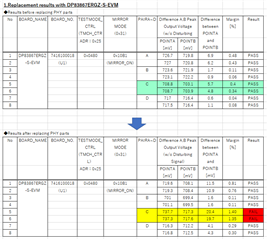

以下部分中的测试失败:

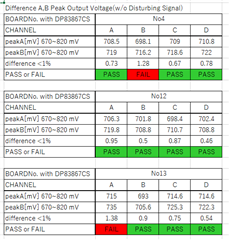

[1000 Base-T、差分 A、B 峰值输出电压(无干扰信号)]

有关详细信息、请查看随附文件。

如有关于合规性测试结果的任何建议、我们将不胜感激。

【Question1】

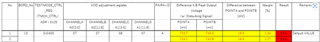

上述 No.4_Board 以及 No.12_Board 和 No.13_Board 仅在 PHY 器件上有所不同。

根据上述测试结果、我认为可能会因元件而导致端口差异 A、B 峰值输出电压发生变化。

您能告诉我如何改进以上内容吗?

【问题2】

我检查了与此问题类似的主题。

但我不知道如何改进它。

您还可以在 E2E 社区中看到一个有关此问题的话题、但这是一个私有通信、我不了解解决方案。

您能否分享您解决此问题的解决方案?

:e2e.ti.com/.../dp83867ir-10base-te-100base-tx-1000base-t-compliance-test

此致、