主题中讨论的其他器件: TMDS1204、TDP1204

工具与软件:

您好!

我们在 HDMI 设计中使用了 ds125。 在 HDMI 4K 中,我们需要测试偏斜(每行大约112ps )和抖动(关于 数据线500kHz;时钟线 10 MHz )、您是否在?之前完成了该测试

此致

杨辉

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

您好!

我们在 HDMI 设计中使用了 ds125。 在 HDMI 4K 中,我们需要测试偏斜(每行大约112ps )和抖动(关于 数据线500kHz;时钟线 10 MHz )、您是否在?之前完成了该测试

此致

杨辉

感谢您的答复。

让我详细解释一下我们的问题:

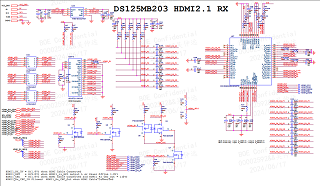

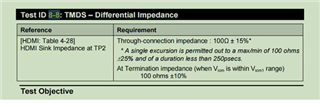

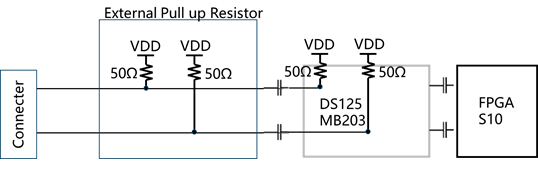

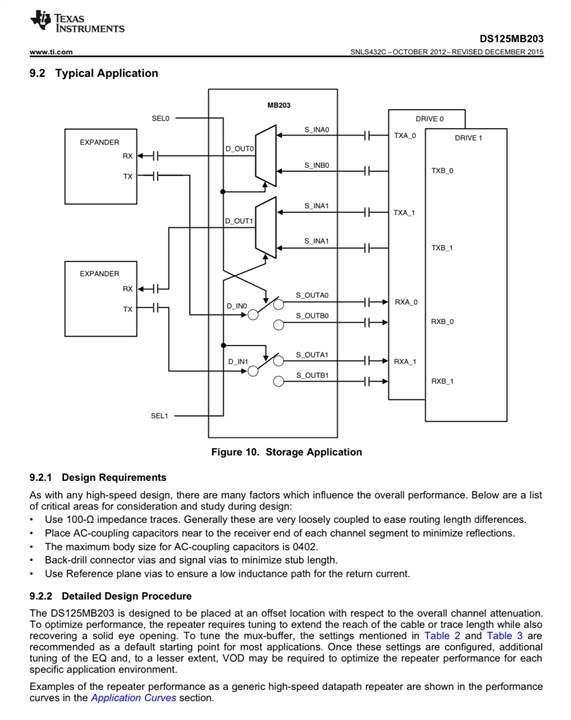

下面是我们的设计原理图。 我们将 DS125MB203与 Altera S10搭配使用、用于 HDMI 2.1连接、硬件设计如下 . 我们正在做 HDMI CTS (合规性测试规范)。

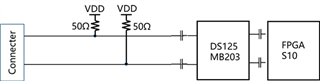

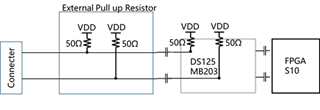

设计原理可简化为

我知道此连接基于 Tx 驱动器的 CML 模式。

HDMI CTS 标准要求在断电模式下、HDMI 输入的终端阻抗应该无限大。 但在此连接模式下、测得的阻抗为100 Ω。

为了通过此要求、我们将上拉电阻器更改为500 Ω。 但通过这种连接,在 HDMI TMDS 测试模式下,信号无法被 DS125识别,无论我们如何调谐 EQ/DEM 等。 如果我们将上拉电阻器从500欧姆更改为250欧姆、则可以识别信号、并且通过使用 FF 调整 EQ 也可以通过差分对间偏移和抖动测试、仅150mV 最小摆幅测试失败。

端子阻抗似乎匹配不佳、会导致信号质量不佳。 但如何在断电模式和加电模式下满足端子阻抗要求?

亲爱的卢卡斯:

非常感谢您的奉献。 让我补充解释一下我们的问题。

对于 HDMI CTS 标准、在断电模式下、HDMI 输入的终端阻抗无限大。 在上电模式下、HDMI 输入的终端阻抗为100 Ω。

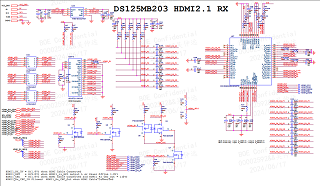

在 DS125MB203数据表中、我们发现输入端具有片上上上拉50Ohm 电阻。 系统图如下所示:

下面是这个问题、在这个设计(Intel 推荐的设计)中、在加电模式下、测得的输入阻抗为50 Ω(两个并联连接的100 Ω)。

我们发现、通过增加外部上拉电阻器、VCM 发生了偏移(例如、VCM=2.0V、使用240Ohm 外部上拉电阻器)

我们认为、由于 DS125已经具有片上50 Ω 电阻、因此应该无需添加外部上拉电阻。

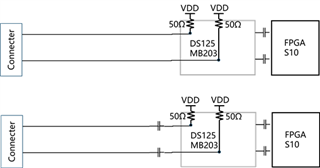

我们可以这样重新设计系统吗?

使用直流耦合结构会带来什么风险?

或者是否可以断开 DS125MB203中的片上上上拉电阻器?

我们将尝试您的建议、即通过将 RESET 引脚拉高并在上电后覆盖 RESET 引脚、以匹配断电阻抗。

许永辉

问题在于、在本设计(Intel 推荐的设计)中、在加电模式下、测得的输入阻抗为50欧姆(两个并联连接的100欧姆)。

DS125MB203的接收器阻抗为50欧姆单端、100欧姆差分。 因此我认为这应满足100欧姆差分的 HDMI 要求。

使用直流耦合结构有何风险?

DS125MB203需要进行交流耦合、以确保没有直流电压到达器件。 因此、不应使用直流耦合结构。

或者是否可以断开 DS125MB203中的片上上上上拉电阻器?

是的、这是可能的、但我们通常不建议这样做。 我仍然很难理解、在此设置中、通电模式下有什么问题? 阻抗是否不是100欧姆差分? 断开片上上上上上拉电阻器将如何解决该问题?

、我们将尝试向高电平拉高 RESET 引脚并在上电后覆盖 RESET 引脚以匹配断电阻抗的建议。

为了澄清这一点、我建议将 RESET 引脚拉至高电平或通过寄存器写入覆盖 RESET 引脚。 我在原理图上看到、将 RESET 引脚拉至高电平可能很困难、因此更容易实现使用寄存器写入进行覆盖。

此致!

卢卡斯

DS125MB203的接收器阻抗为50欧姆单端、100欧姆差分。 因此我相信这应该能满足100欧姆差分 HDMI 的要求。[/引述]由于都有外部100欧姆差分 和片上100欧姆差分、因此它们是并联的。 因此、测得的总差分阻抗为50欧姆、并且采用外部100欧姆差分时、在断电模式下、测得的差分阻抗不是无限的。

为了澄清这一点、我建议将 RESET 引脚拉高或使用寄存器写入覆盖 RESET 引脚。 我在原理图中看到、将 RESET 引脚拉至高电平可能很困难、因此更容易实现寄存器写入覆盖。如果使用寄存器线覆盖复位引脚、那么断电时寄存器设置仍然有效?

[/quote]

许永辉

接收器输入端的内部上拉电阻为50 Ω。

由于同时存在外部 100欧姆差分和片上100欧姆差分、因此它们是并联的。 因此、测量的总差分阻抗为50欧姆、而且在断电模式下、使用外部100欧姆差分、测量的差分阻抗不是无限的。[/报价]我相信您在这里的理解是错误的。 在内部、接收器引脚具有100欧姆差分阻抗。 外部布线还需要具有100欧姆差分阻抗以匹配内部阻抗。 内部和外部上拉电阻器不会并联。 所示的原始设计正确、可保持100欧姆差分阻抗。

关于断电模式:是否可以关闭外部 VDD 电源? 这将使外部差分阻抗变得无限大。

通过使用寄存器 wirtes 覆盖复位引脚、断电时寄存器设置仍然有效?我不确定我是否理解这里的问题、请允许我澄清一下。

- 如果您的意思是、当通过覆盖 RESET 引脚对个别通道断电时、寄存器设置是否仍然有效? 答案是肯定的。

- 如果是这样、当 DS125MB203器件断电后、寄存器设置是否仍然有效? 答案是否、寄存器设置将复位。

现在我已经更好地了解您的系统和问题、我不确定这种方法是否能够在断电模式下实现无限阻抗、因为仍然存在外部上拉电阻器。 我认为您需要关闭外部 VDD 电源。

此致!

卢卡斯

[/quote]

我认为您的理解不正确。 在内部、接收器引脚具有100欧姆差分阻抗。 外部布线还需要具有100欧姆差分阻抗以匹配内部阻抗。 内部和外部上拉电阻器不会并联。 所示的原始设计是正确的、并保持100欧姆差分阻抗。

我有不同的看法、认为终端电阻仅用于匹配传输线路阻抗。 在这种情况下、内部上拉电阻器用作端接电阻器、无需添加另一个外部上拉电阻器。 并且我们从测试 设备(Keysight9505A)测量了50 Ω。 它使我们感到困惑。

在 DS125数据表中、应用无需外部上拉电阻。

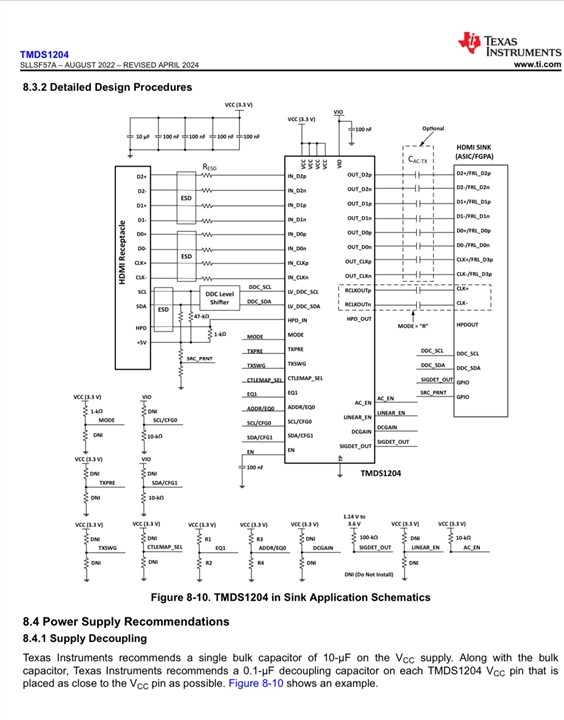

我们还可以查找标准 HDMI 转接驱动器 TMDS1204应用。 也无需外部电阻器。 (不知道为什么英特尔在 HDMI 应用程序中推荐 DS125、这让我们感到疯狂)

如果是指、在 DS125MB203器件断电后、寄存器设置是否仍然有效? 答案是否、寄存器设置将被重置。

这就是我的意思、在断电模式下、寄存器设置将被擦除。 我们无法保持 DS125MB203的无限输入阻抗。

如果我们使用直流耦合应用会怎么样? DS125无法正常工作? 我想这是我们最后的希望。

大家好、Lucas:

DS125MB203不适用于 HDMI 应用、

是否有任何参考设计案例将 TMDS1204/TDP1204与 Intel S10/A10 FPGA 应用于实现 HDMI 应用? 如果有、请告知我们详细信息。 谢谢。

我想 就此得出一个结论。 DS125MB203不是为 HDMI 应用而设计的。 当 Intel 开发 HDMI 应用时、还没有专门的 HDMI 重定时器、因此他们选择了 采用 DS125MB203的子板。 他们承认 从未 通过 HDMI 合规性测试(CTS)。 DS125MB203的主要问题是它 只能支持 交流耦合输入、这不适合 HDMI 接收端所需的直流耦合输入。 因此、很难匹配输入阻抗、从而导致相对较差的信号质量、尤其是在高速模式下。 英特尔已开始 采用 TMDS1204重新设计新的重定时器解决方案、并修改了 HDMI 应用的设计指南、但尚不清楚何时会完成。 对于那些只需开发 HDMI 应用演示的设计人员、可继续将 DS125用作重定时器。 但是、如果您的产品需要通过 HDMI CTS 认证、根据我们的经验、建议 是:尝试其他选择。