主题中讨论的其他器件: DP83869

工具与软件:

您好!

我们将 DP83869HM 用于以太网 PHY、现在、数据表 说明中有一些问题:

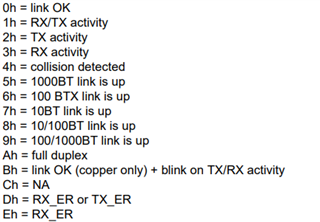

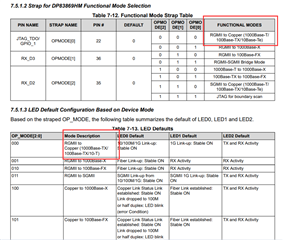

1.阅读数据表7.5.1.2和7.5.1.3、我们想知道 RGMII 转铜缆是否支持1000Base-TX?

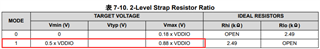

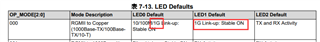

2.阅读产品说明书、LED1是2级 strap 配置、TARGETVOL Vmin = 0.5VDDIO、MODE1时 Vmax = 0.88VDDIO;

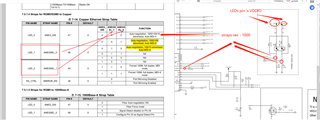

PD = 9K Ω 时、根据数据表7.5.1.2、

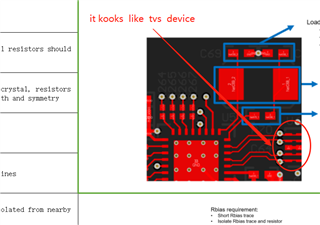

我们 按如下公式计算 LED1电压:(LED 电阻器470 欧姆、电阻器2.49k 欧姆并联、LED 传导电阻考虑为100欧姆)、

Vled1=(9K/(470欧姆+100欧姆)//2.49Kohm+9K)* VDD VDD=0.95VDD,0.95VDD大于0.88VDD,请 提供 该设计的原理;

工作原理

3. Plesae 可用于设计 RGMII RX_CLK 延迟和 TX_CLK 延迟 寄存器或硬件配置设置、 或者如何设置数据以确保时序正确性? 谢谢。