Thread 中讨论的其他器件:TLK105、 AM5728

工具与软件:

关于审判问题的专题

1.1背景

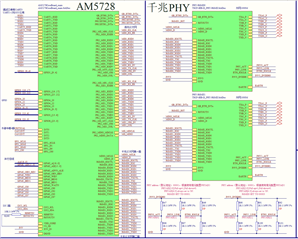

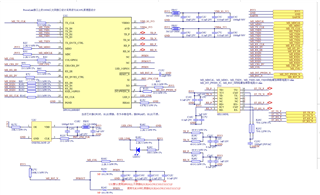

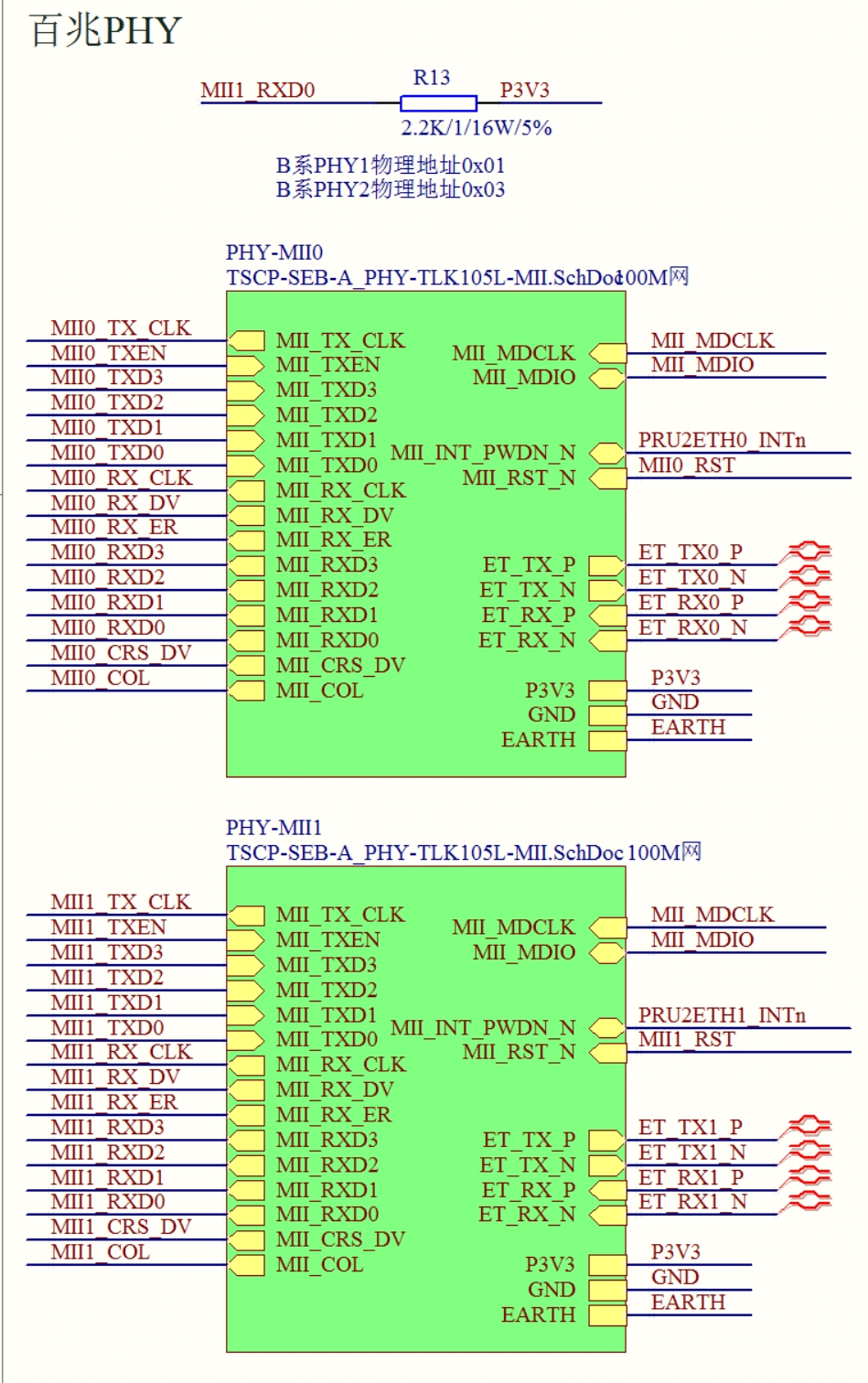

在测试中、我们发现通信控制板和串行端口扩展板(与 PCB 相同)在温度变化期间不响应100千兆位网络 ETH3故障。 原理如下:CPU 通过 SMI 总线访问 PHY1/2、PHY 的地址为0x01和0x03。

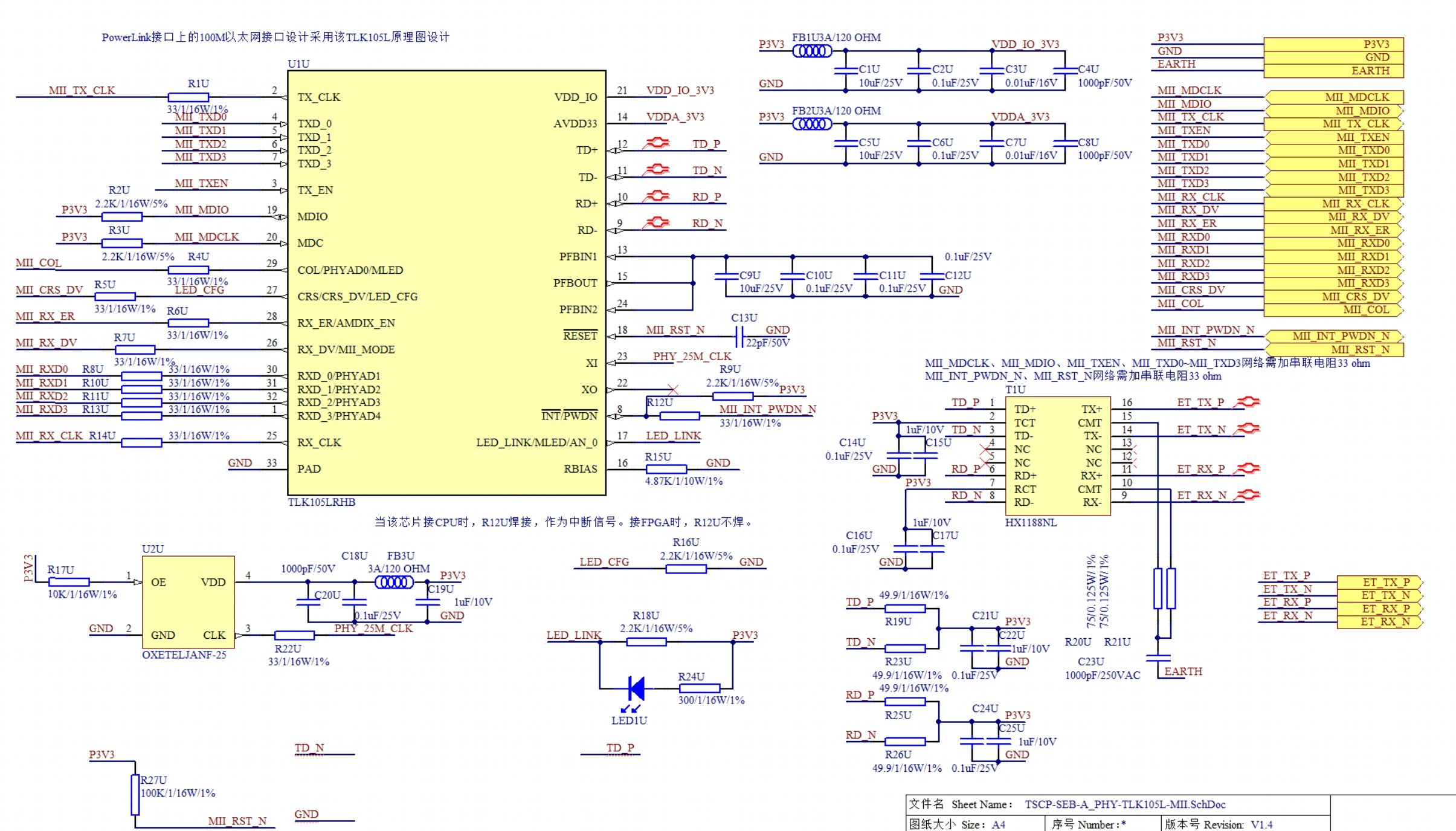

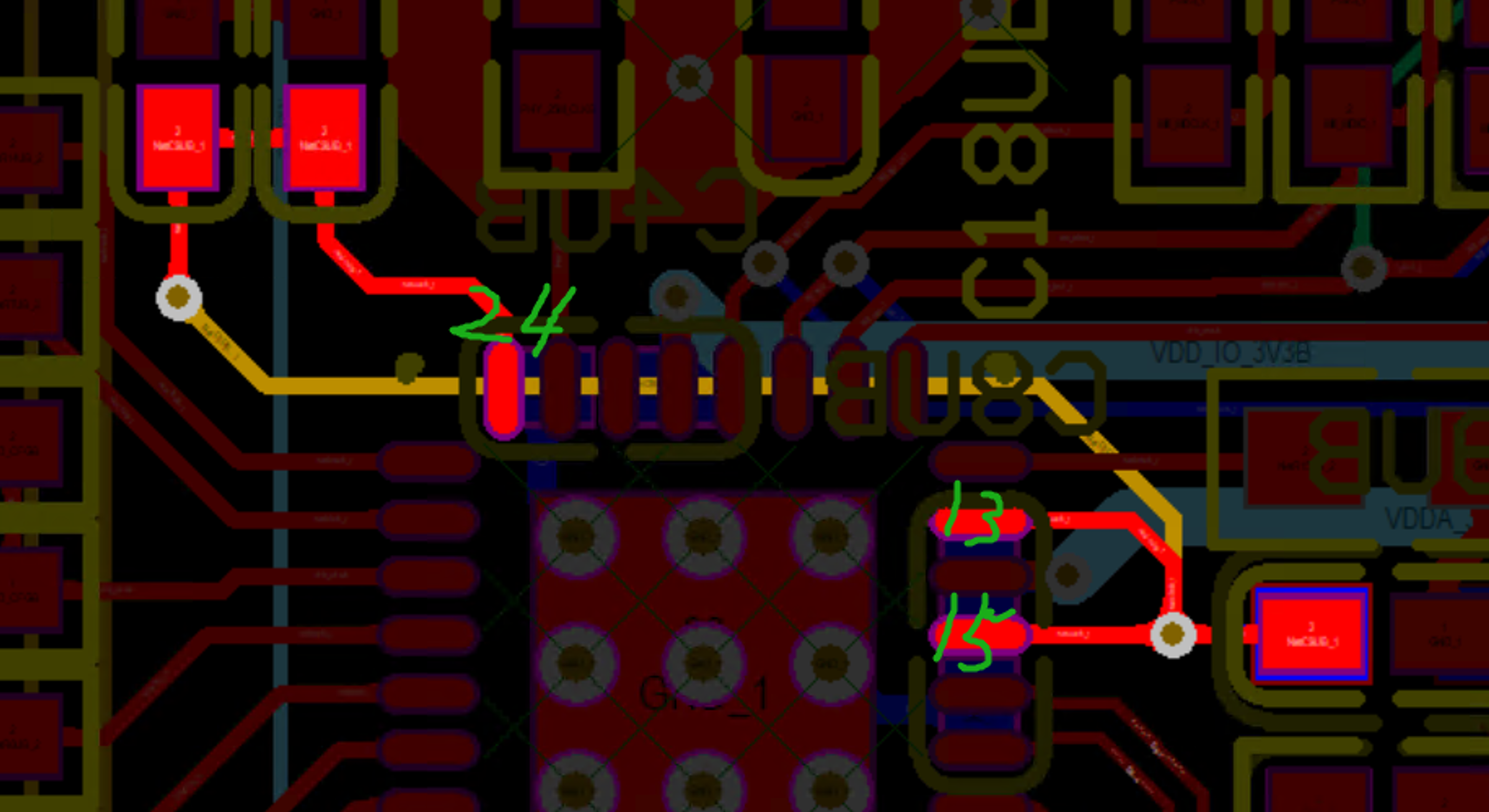

重复使用 TLK105的原理图、PHY 的内部点如下所示。 但83822已经过调整、并且83822 NC 引脚上的相关器件已被删除。

卸下外围设备后、三个引脚通过一条线路连接、如下图所示:

1.2. 测试问题现象

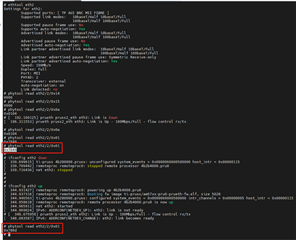

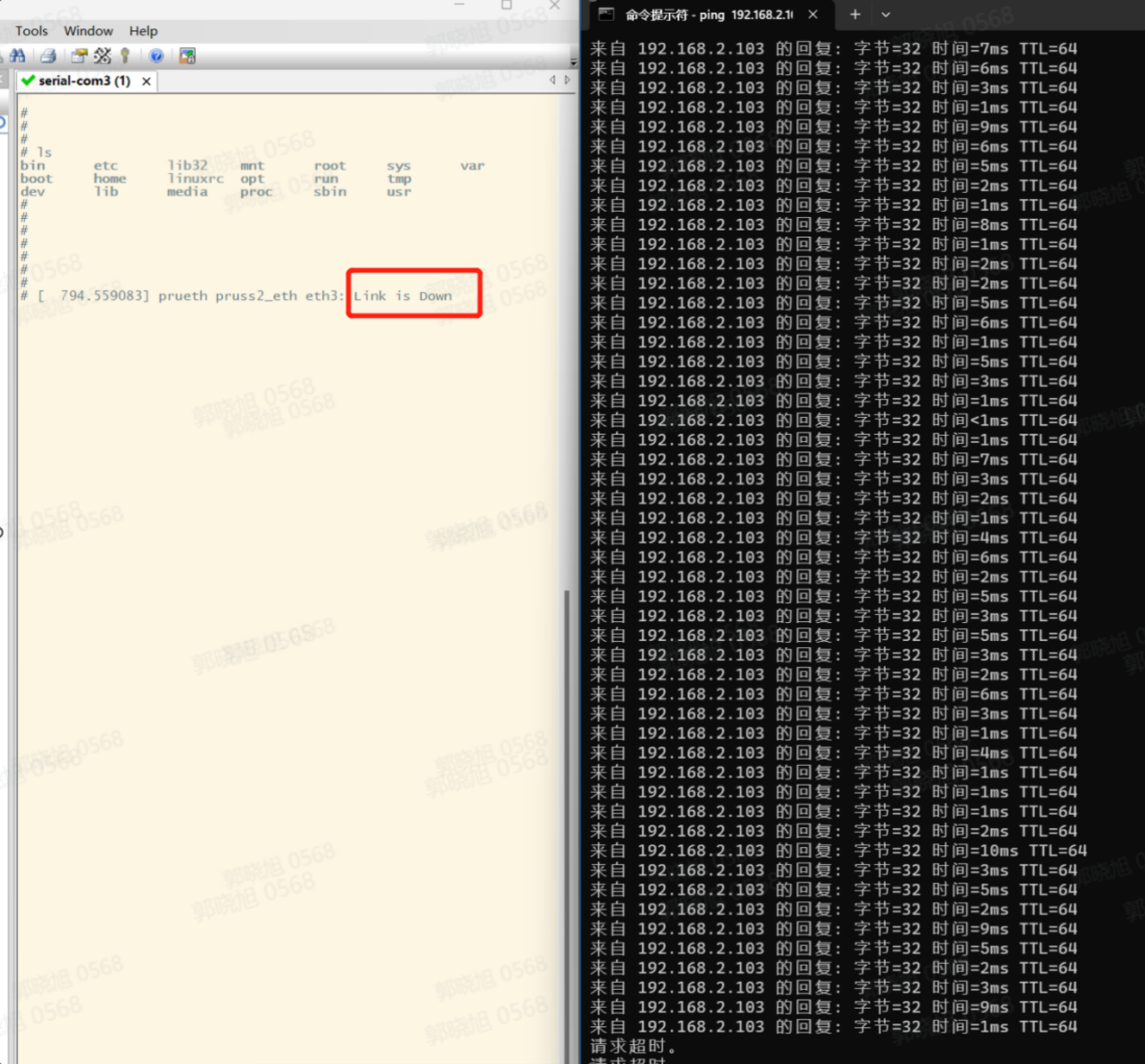

根据 HASS 测试的要求、TSCP 主机 Subrack 需要放置在 HALT 测试室内、用于从-25°C 到60°C 的温度循环、并辅以振动。 在-20°C、单个通信控制板的 eth3网络会中断、无法实现通信、ping 也会中断。

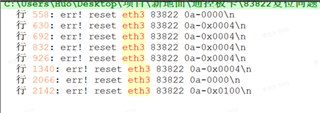

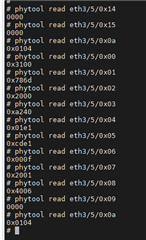

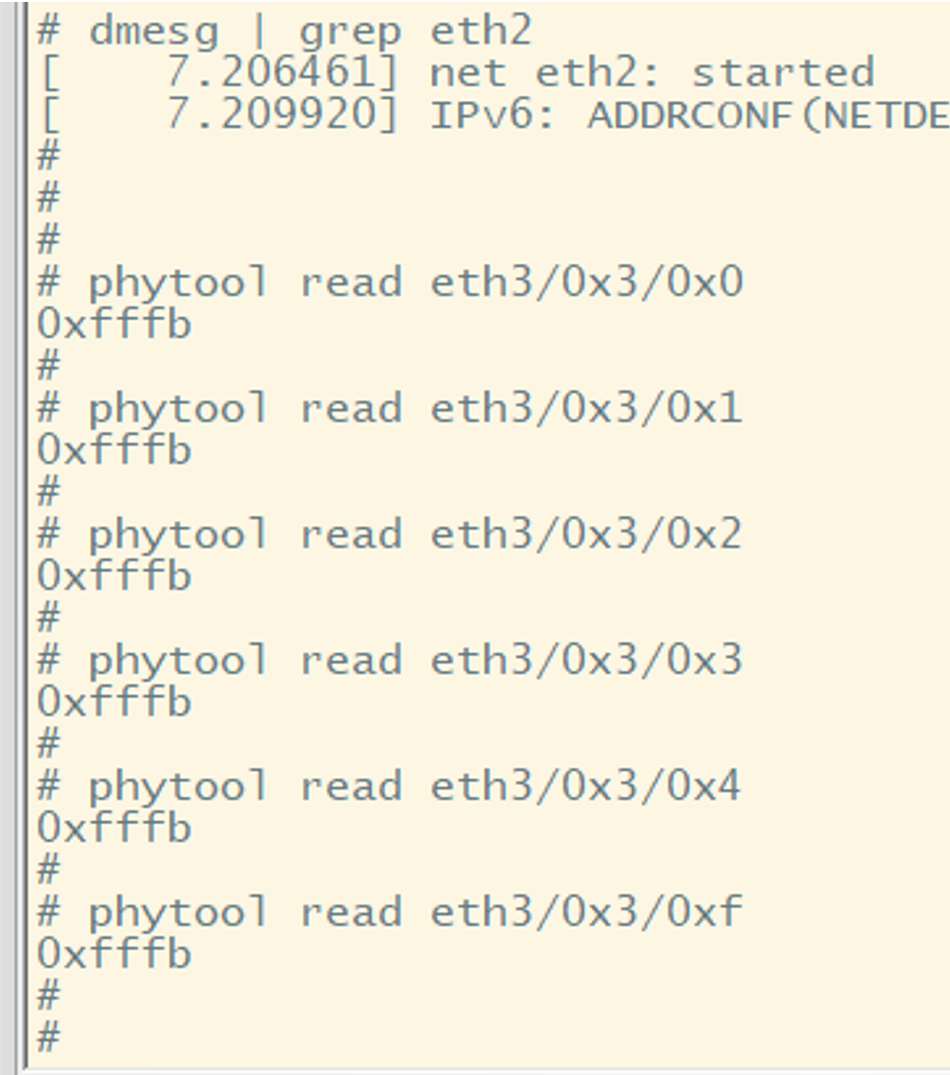

读取 ETH3的寄存器状态、发现所有 PHY 寄存器均无法读取。 当操作系统的底层轮询 PHY 地址0到31时、会发现 PHY 地址消失、并且无法访问该 PHY 的所有寄存器。

针对去年在室温下 PHY 无法读取后、TLK105替换为83822芯片的问题分析显示、这一现象与当时的情况是一致的。

1.3. 对问题进行修改调整和测试验证

1.3.1. MDC 波形

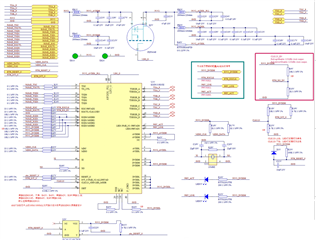

通过修改 MDC 和 MDIO 接线、已知方案可以解决信号干扰问题、但从根本上解决不了干扰源。 因此、根据上面的电路、通过调整电源输入和输出端子的电阻、电容和电感、更换电源模块来执行信号测试。 测试记录如下:

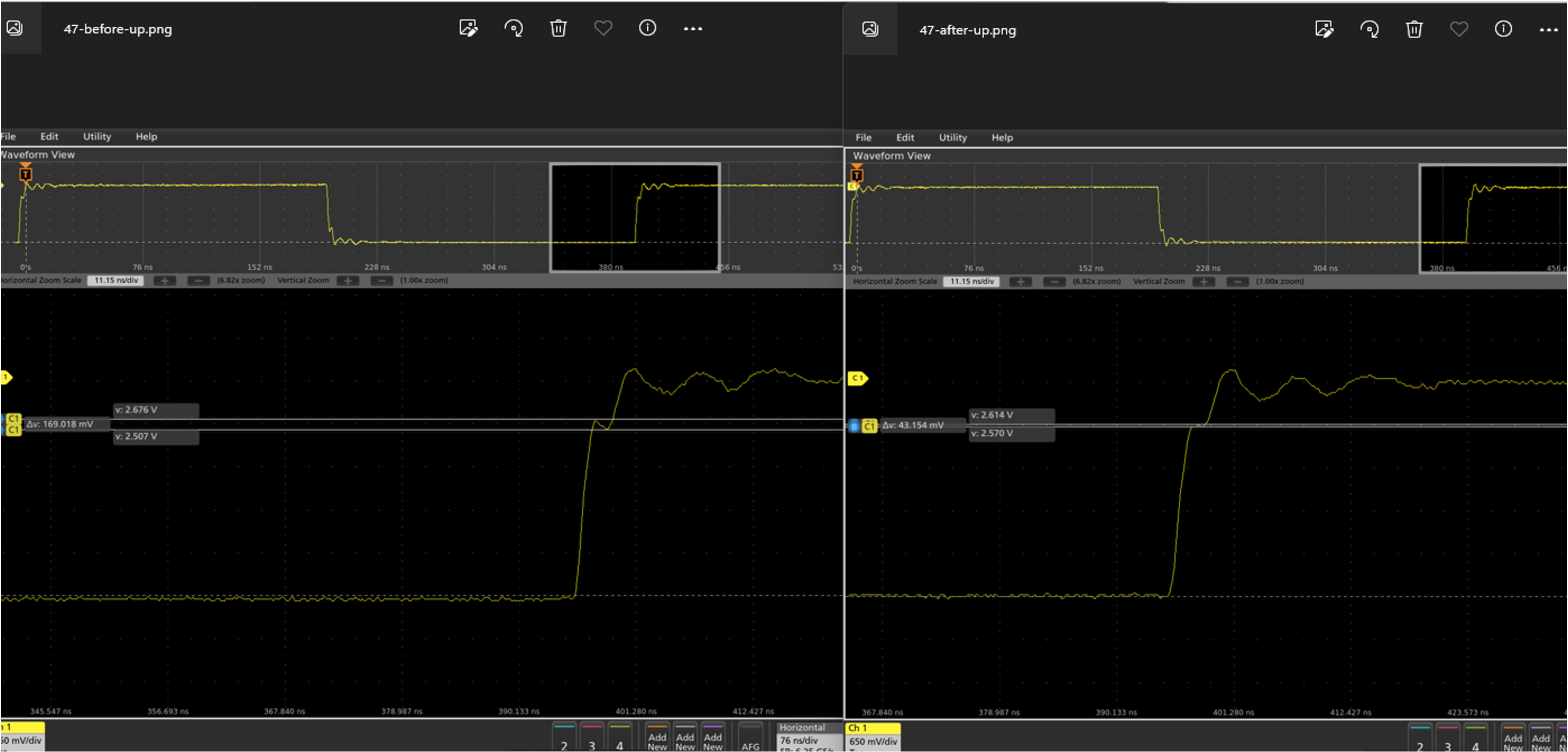

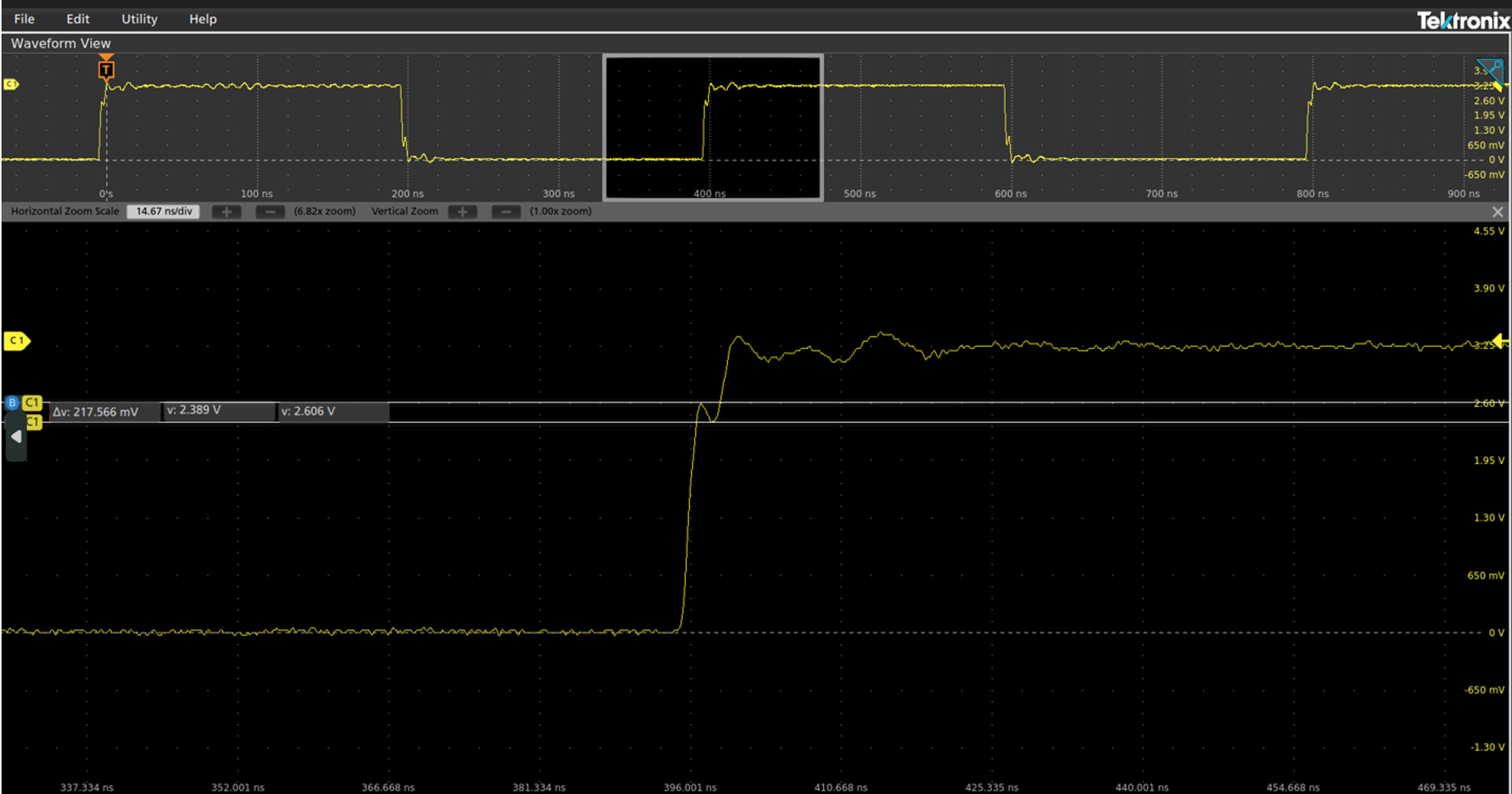

波形不良:

更好的波形:

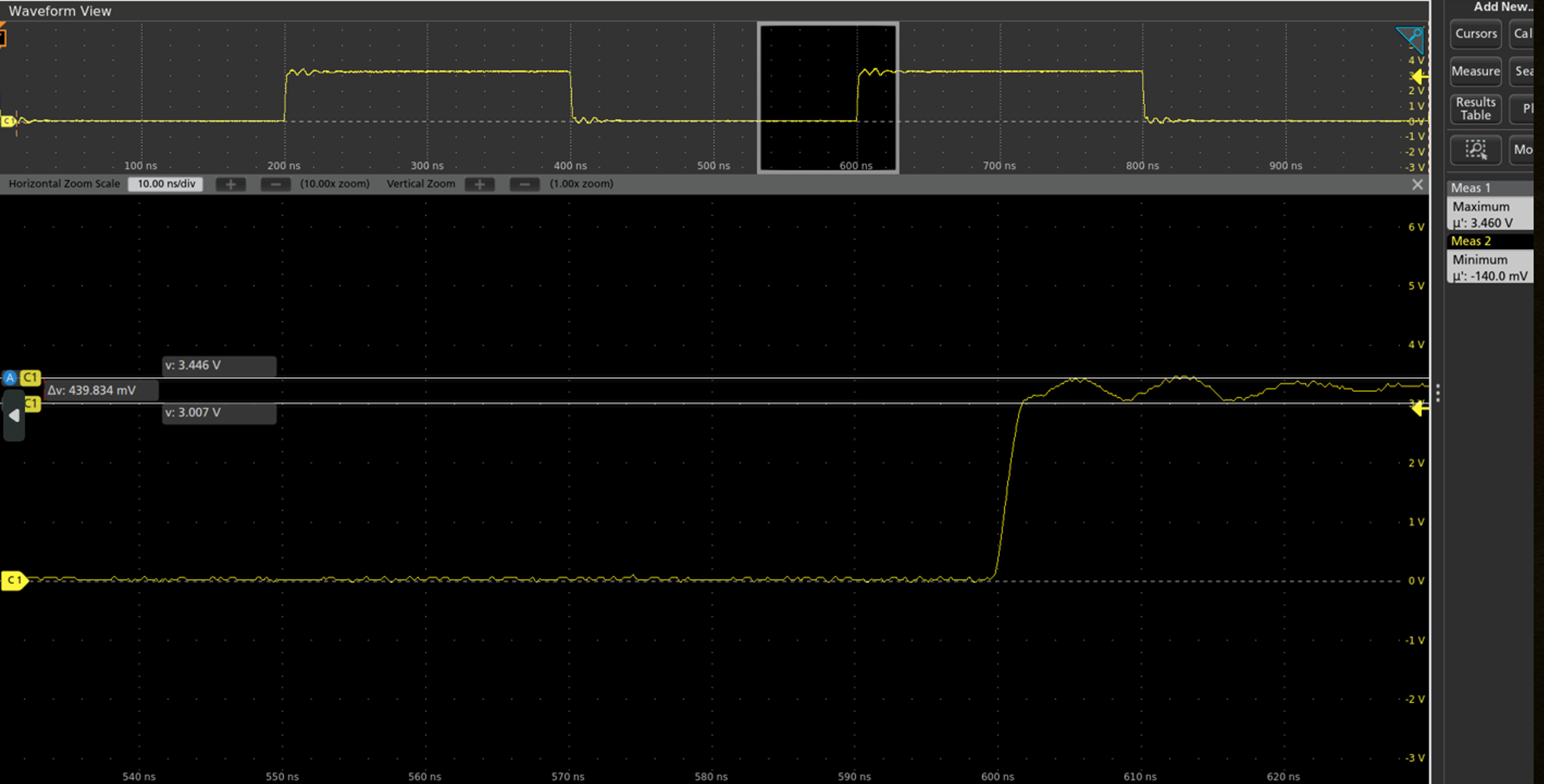

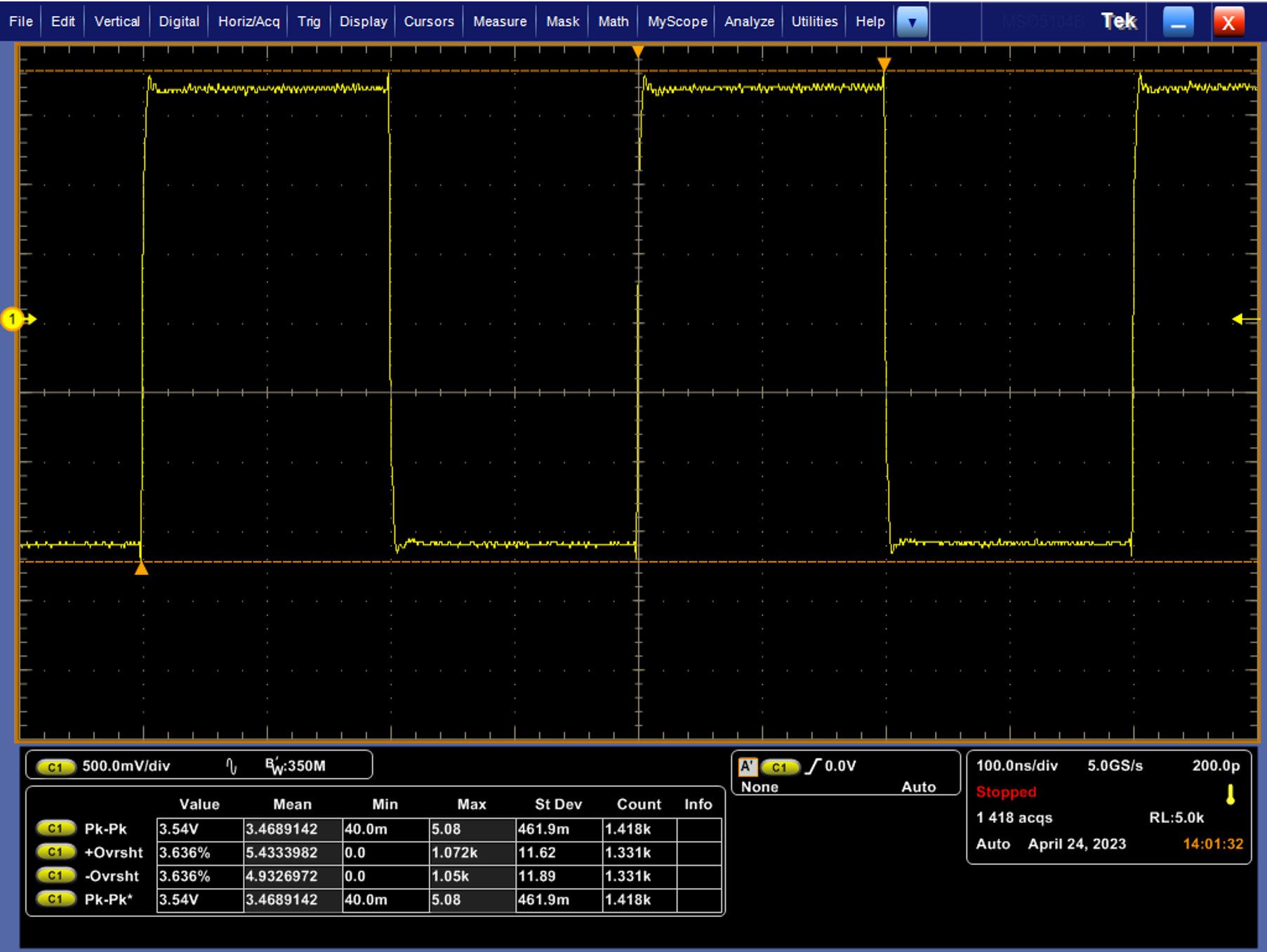

在此波形调试的基础上、我们修改了 PCB 的一个版本、修改后的版本具有更好的测试波形、如下图所示:

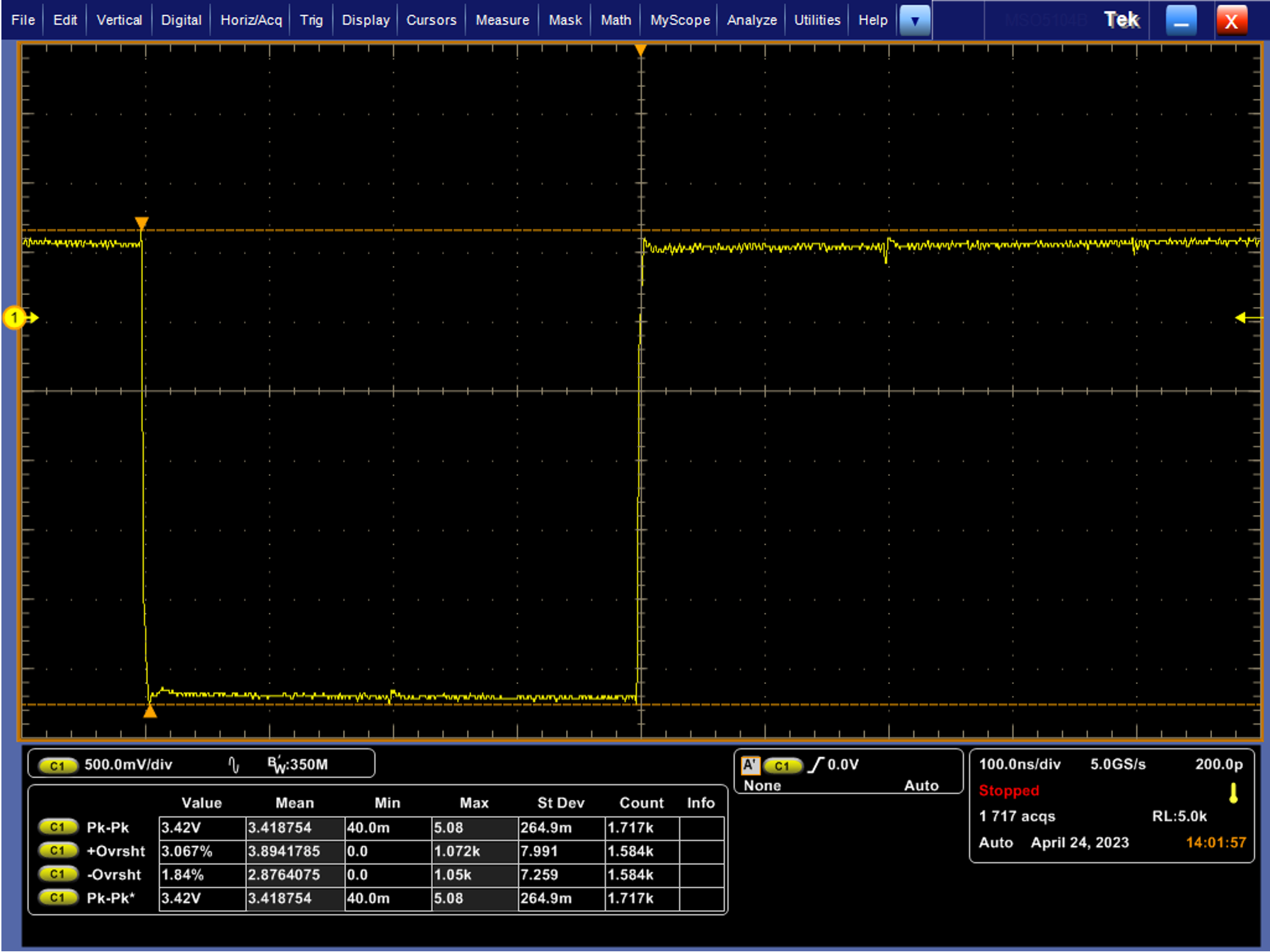

SMI 总线的信号波形测试如下:

MDC:

MDIO:

整体波形不错、与多电容方案相比、该波形的 MDC 过冲略大约1%、但通过修改布线、信号质量仍然得到改善。

经过500轮测试、PHY 未出现问题、硬件在此版本中完成。

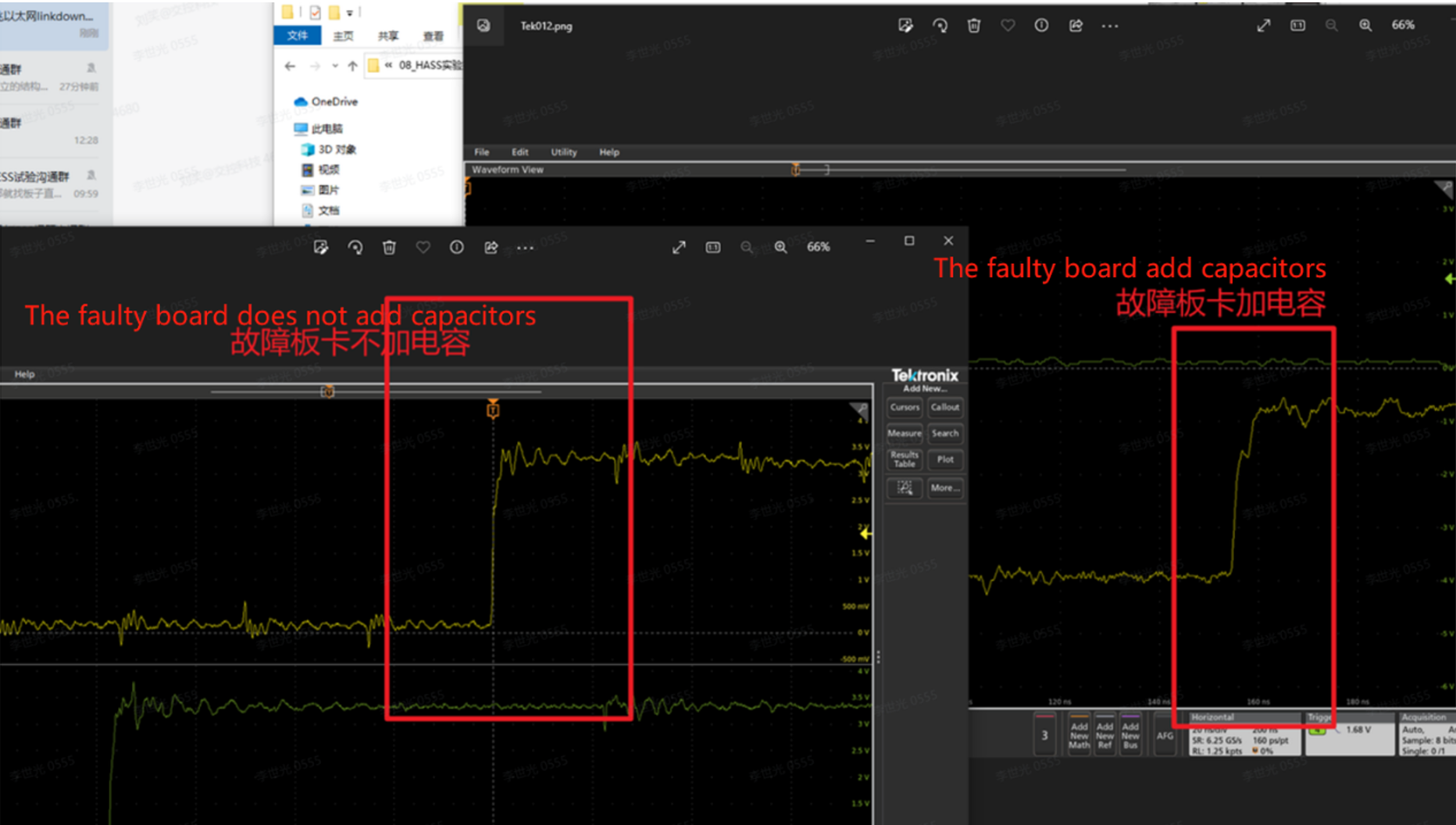

但是、在常规生产中更换 PCB 并将电容器添加到 MDC/MDIO 之后、也会出现类似的信号质量问题。 但是、由于无法修改 PCB、电容器上拉至 VCCIO、该测试确实解决了此版本 PCB 的 PHY 压降问题。 已生产的电路板将根据该计划进行整流。

更新版本的 PCB 是根据下拉电阻器方法重新绘制的、并进行了后续电路板生产。

然而、最近、在老化实验中、有一批在 MDC/MDIO 信号线上带有上拉电容方案的电路板有 PHY 断开的问题。 断开连接的性能与之前相同。

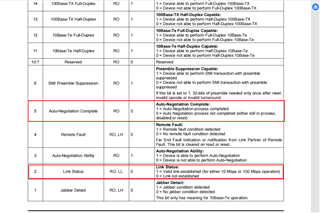

目前、主要问题是断开连接后无法确认 PHY 所处的状态、并且无法通过寄存器访问获取 PHY 的故障流程。 网络只能通过 PHY 的硬复位信号恢复为服务。 这种情况的原因可能是什么?如何进一步找到故障原因?