工具与软件:

专家、您好!

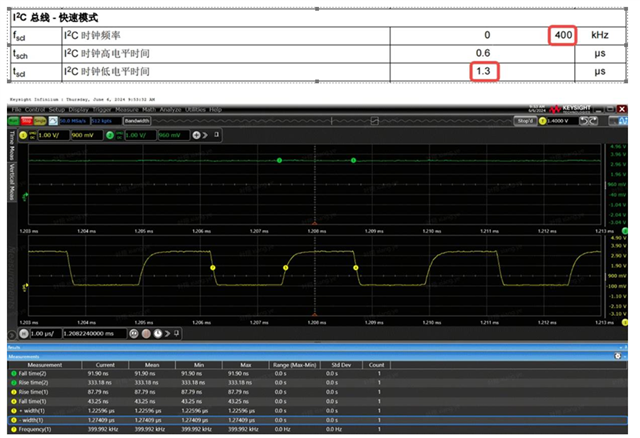

我的客户测试 IIC 总线相关参数、发现 SCL 低电平时间不符合 TCAL9539-Q1的从器件标准。 Jacinto、TDA4 SOC 附带了一个设置为 IIC 50%占空比的 SDK 或内核驱动器。 SCL 低电平是1/(400K*2)=1.25us。 这不符合1.3us 的最低要求。 如果不符合此参数标准、风险有多大? 如果满足要求而不接受频率降低、那么是否存在修改自包含驱动代码中相关的高电平和低电平时间寄存器值的风险? 或者是否存在在自驱动配置完成后修改用户应用程序代码中关联的高/低电平时间寄存器的值的风险?

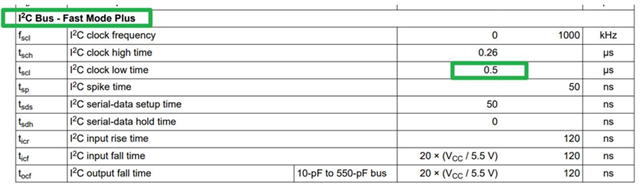

客户无法使用超快速模式、因为该模式需要1.8V 电源、并且我客户的硬件是固定的。 即使频率可以是1MHz,SCL 低为 1/(1M*2)=0.5us ,也没有裕度。

此致、

文廷