工具与软件:

您好!

我们看到了 我们在电路板上使用的 SN65LVDT33器件的一个意外问题、其中我们在通过其发送例如75MHz 时钟(LVDS->SE)时看到芯片输出信号的抖动高于预期:

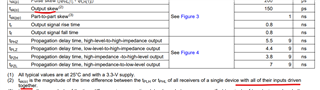

= SE 输出、包含+- 1ns 抖动。 (片上驱动2个信号)

= SE 输出、包含+- 1ns 抖动。 (片上驱动2个信号)

== LVDS 输入-极低的抖动(片上驱动2个信号)

== LVDS 输入-极低的抖动(片上驱动2个信号)

(我们没有看到 LVDS 上的抖动进入芯片)

有趣的是、如果使用此75MHz 信号驱动芯片的4个通道之一、抖动就会消失。

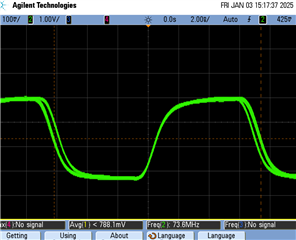

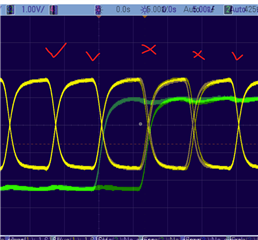

该场景现在用于轻松地演示此行为、在一个 LVDS 对上发送10MHz 时钟、在第二个 LVDS 对上发送75MHz 时钟(黄色)。

获取一些更多示波器图像后、可以清楚地看到75MHz 线上的"毛刺脉冲"具体发生在另一条10MHz 线(绿色)经历上升沿转换时。

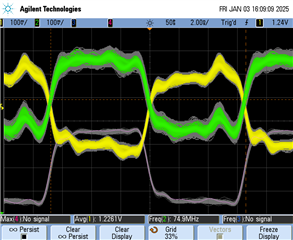

下图是在慢速信号上升沿触发的捕获、叠加在自身上并在油漆中移位。 您可以看到75MHz 周期最初是如何非常干净的、当缓慢/绿色信号的上升沿"耦合进来"时、75MHz 信号的上升沿略有延迟、从而导致抖动效应(在上面更简单的示波器图像中也可以看到这一点、由示波器本身"叠加"、但未显示与另一个信号的确切相关性)。

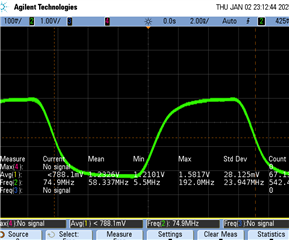

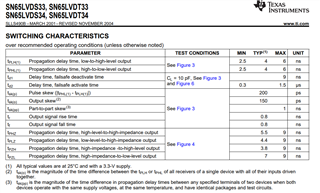

数据表列出了以下限制

实际上、我们预期会出现大约150ps 的抖动-而不是现在看到的1000 ps 的抖动。

这是一个已知限制吗? 这种行为对我们来说有点令人振奋。

提前感谢您的反馈!

此致、

Arnout