主题中讨论的其他器件:CDCEL913

工具与软件:

尊敬的专家:

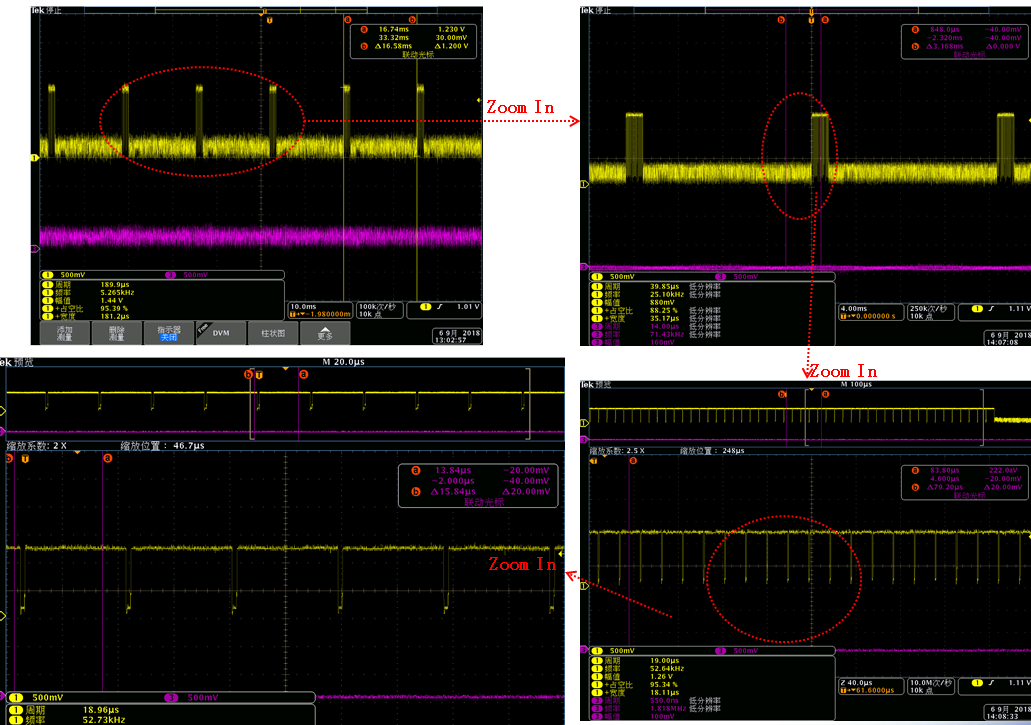

目前、我们将 DSI 时钟用于 SN65DSI-Q1、并且随机遇到间歇性白屏问题。 为了解决这一问题、我们实现了 CDCEL913参考时钟、以确保 LVDS 转换器具有稳定的时钟源。 但是、调整寄存器值后、我们现在遇到没有图像输出的完全空白显示。

显示时钟频率为62.58 MHz (典型值)、我们测试了60 -70 MHz 范围内的各种 REF_CLK 频率、但显示器保持空白。

我在下面添加了 i2cdump 值、以供您参考。

00:35 38 49 53 44 20 20 20 01 00 04 00 01 00 58ISD ?..

10:26 00 26 00 00 00 00 00 78 00 03 00 00 00 00 00 00 00 00 00 & X

20:00 05 00 00 00 00 00 00 21 00 00 0A 00 00 00 00 ? !???

30:0C 00 00 00 19 00 00 00 00 00 00 00 00 00 00 00 00 00 ?………………………………

40:00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

50:00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

60:00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

70:00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

80:00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

90:00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

A0:00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

B0:00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

C0:00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

D0:00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

E0:00 00 00 00 f1 00 00 00 00 00 00 00 00 00 00 00 00 ?..........

F0:00 00 00 00 40 00 00 80 00 00 00 00 00 00 00 00 00 @………………………………………………

您能否帮助确定该问题的根本原因并提供可能的解决方案?

提前感谢您的帮助。

Devathi Mahesh。