Other Parts Discussed in Thread: SN65DSI84-Q1, SN65DSI84

Thread 中讨论的其他器件: SN65DSI84

工具与软件:

您好、TI 专家

客户对 SN65DSI84-Q1输出有疑问。

-应用: 视频分离器和通道显示设备

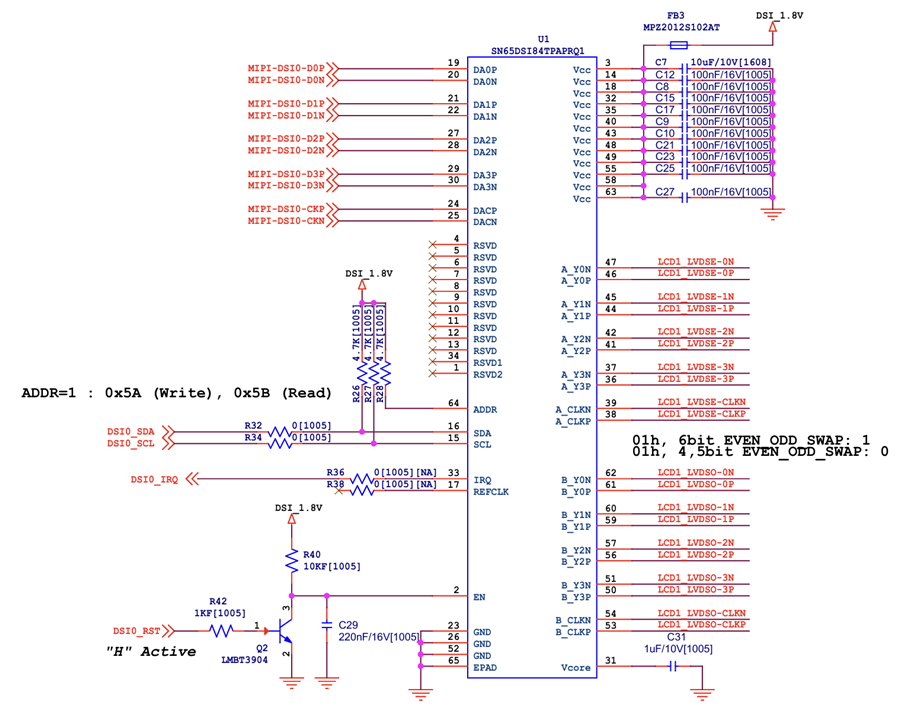

当前的硬件配置如下。

- RK3568 DSI 输出(单路)-> SN65DSI84TPAPRQ1 (双路 LVDS 输出)-> LCD 面板(分辨率1920x360)

[审查和问题]

1) 当 RK3568 DSI 输出设置为1920x1080时、屏幕将正常显示在 LCD 面板上。 (但是、仅显示1080屏幕的顶部1/3。)

2)当 RK3568 DSI 输出设置为1920x360时、LCD 屏幕显示异常(请参见下图。)

视频显示时序如下、并附加 SN65DSI84TPAPRQ1设置值。

Clock-frequency =<142380000>;

hactive =<1920>;

前沿=<60>;

HSYNC-LEN =<60>;

后沿=<60>;

vactive =<360>;

vfront porch=<120>;

vsync-len =<530>;

vback-porch =<120>;

HSYNC-ACTIVE =<0>;

VSYNC-ACTIVE =<0>;

[问题]

Q1) SN65DSI84TPAPRQ1是否不支持1920x360分辨率 LCD?

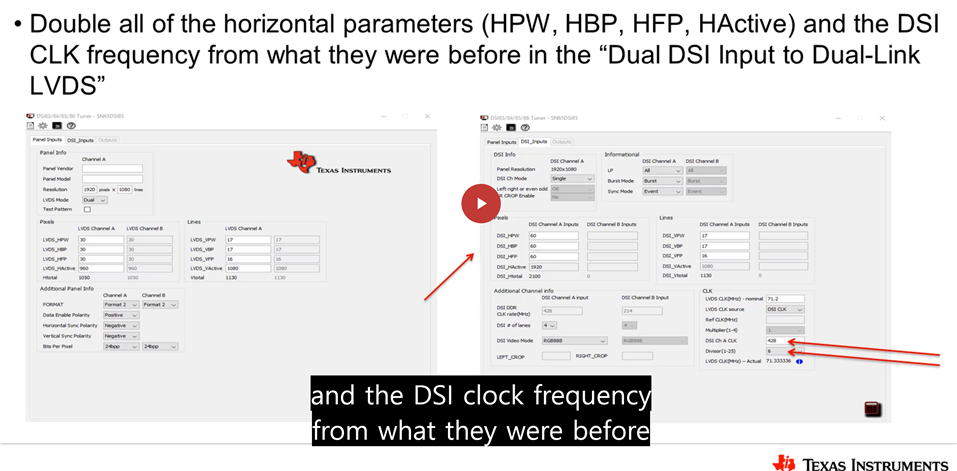

Q2)如果支持它、我如何将其设置为正常输出? (目前、SN65DSI84TPAPRQ1 IC 设置是使用 TI 提供的软件工具完成的。)

请检查。 谢谢你。