工具与软件:

您好!

我们的产品使用 sn65dsi84作为 Linux CPU 模块(将 MIPI-DSI 输出至双通道 LVDS 面板)上的网桥。

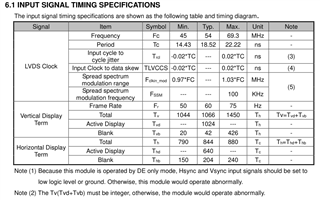

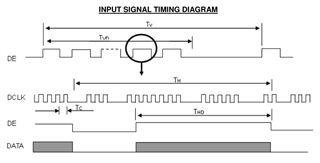

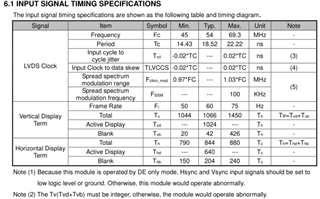

面板数据表规定如下:

"由于该模块是通过仅 DE 模式运行的、因此 Hsync 和 Vsync 输入信号应设置为低逻辑电平或接地。 否则、此模块会异常运行"

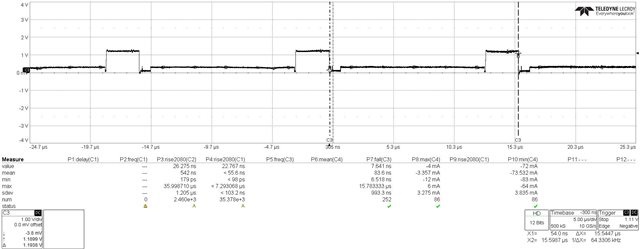

实际上、为了使面板显示我们的引导标识、我们必须将 Linux 驱动程序和硬代码 Hysnc/Vsync 脉冲宽度寄存器修改为0。 这样,我们就可以"模拟"他们不能被使用的事实;没有这个小技巧,屏幕就会变成空白。

我想了解我们的"解决方案"是否是针对此类情况的预期解决方案、或者是否有更好/正确的方法来实现? 我要特别问这个问题、因为我们看到位0xE5.7设置为1、根据我的理解、可以忽略此设置、因为我们不依赖于 HS/VS。

提前感谢您!