您好,

我们正在使用ISO7341C进行RS485隔离。

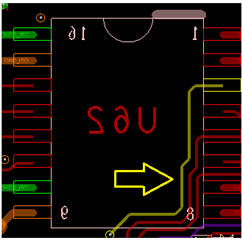

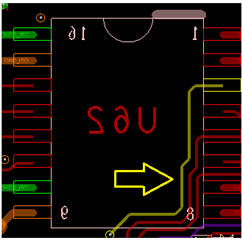

由于布局限制,我将DE,TXD和RXD布置在ISO7341C正下方的底层,如图所示:

我猜这条路由会降低隔离能力。 但由于我需要隔离作为功能隔离,而不是接地回路,所以我对此并不担心。

我想知道的是,这条路线能否更改 ISO7341C的功能? 它是否会导致其他问题?

就我所知,它是否会降低隔离能力?

感谢您的帮助,

亚萨夫·亚伯拉罕

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好,

我们正在使用ISO7341C进行RS485隔离。

由于布局限制,我将DE,TXD和RXD布置在ISO7341C正下方的底层,如图所示:

我猜这条路由会降低隔离能力。 但由于我需要隔离作为功能隔离,而不是接地回路,所以我对此并不担心。

我想知道的是,这条路线能否更改 ISO7341C的功能? 它是否会导致其他问题?

就我所知,它是否会降低隔离能力?

感谢您的帮助,

亚萨夫·亚伯拉罕

您好,Asaf,

感谢您发布到E2E! 由于隔离设备下的路由轨迹,通孔或铜质平面可能会破坏隔离屏障,因此我们通常不建议这样做。 根据系统的功能隔离要求,这可能是可以的,因此请确保相应地测试隔离性能。

关于设备功能,无论信号是否在其下方传输,ISO7341C都应正常运行,不会出现任何问题或设备级性能变化。 设备的电气,定时和隔离规格将保持不变,但是由于隔离屏障的宽度减小(也称为爬电/间隙),系统本身的隔离性能可能会降低。

当隔离器是从器件一侧的引脚到另一侧的引脚(由CLR和CPG规格在其数据表中指定)测量的穿过隔离屏障的最短路径时,隔离器的隔离规范适用于系统。 当信号,通孔或平面缩短隔离屏障与这些值之间的距离时,最大隔离电压额定值可能会降低,尤其是铜暴露在PCB顶部或底部表面时。 隔离性能的变化量取决于相关的隔离参数,指定额定值的行业标准以及隔离挡板中导电材料之间的最短距离。

我希望这能回答你的问题。

尊敬的,

Manuel Chavez