主题中讨论的其他器件:TPS3106-EP

当 Vcco < 2.25V 时、ISO7740F 的输出在数据表的表2中列为"未定"。

是否有任何方法来排列器件(也许使用外部组件)、以便在施加 Vcco 时不会出现毛刺脉冲(变为高电平)? (假设 EN 保持低电平、VCCI 可以断电或以输入低电平通电)

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

当 Vcco < 2.25V 时、ISO7740F 的输出在数据表的表2中列为"未定"。

是否有任何方法来排列器件(也许使用外部组件)、以便在施加 Vcco 时不会出现毛刺脉冲(变为高电平)? (假设 EN 保持低电平、VCCI 可以断电或以输入低电平通电)

Steve、

不用客气! 数据表表中未涵盖具有外部组件的情况、例如下拉或上拉电阻器。 即使输出引脚上的电压不确定、添加下拉电阻也会将输出路径接地。

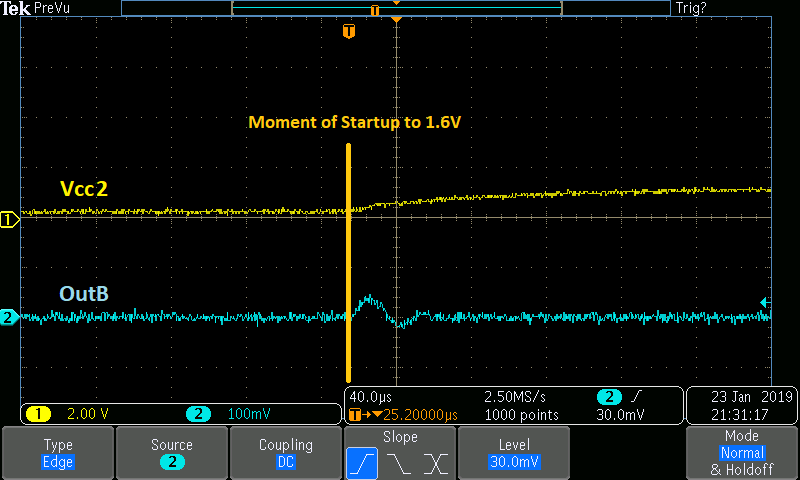

我们希望防止的干扰的振幅和持续时间是多少? 在前面提到的表格条件下进行的基准测试显示、在启动时输出引脚上的电压为300mV 或更低、时序顺序为微秒和纳秒、如下图所示。 由于这些振幅低于大多数阈值、因此预计不会打开任何外部组件。

我将等待您的答复。

谢谢、

Manuel Chavez

P.S. 为了清晰起见,对该帖子的文本进行了编辑

您好、Steve、

上一篇文章中所附的波形是在加电期间捕获的、但从那时起、我无法在实验室中再现波形、以测试我们提出的解决方案。 输出上的摆动因器件间的差异以及 ISO7740F 所处的 PCB 环境而异。 我们的团队建议在输出引脚上使用10kOhm 下拉电阻器来帮助减少电压波、并联添加~0.1nF 的小电容器有助于进一步减少任何电压摆动。 监控器 IC 是一种有效的解决方案、它可能是过度使用的。

我们可以继续测试以检查这些解决方案是否良好;请告诉我您或我们的客户是否希望我们继续。

周末愉快!

Manuel Chavez