Other Parts Discussed in Thread: SN74LV8154, PCM1794A

“线程”中讨论的其它部件:SN74LV8154, PCM1794A

我构建了一个完全离散的基于逻辑的电路,我有这个移位寄存器,它将数据从 SN74LV8154上的 Y 总线转换为串行数据,我的逻辑设计允许移位寄存器加载1个额外位,因此它以 SER 输入的值结束 (保持较低) 在 SH/LD 再次变低之前,但输出结果似乎是随机状态,与输入无关,输入可能高或低,如果高,输出将缓慢向下压,同时以远远高于10MHz 时钟源的高频率振荡。

我有4个计数器,其中一个计数器的 RCOA 与时钟连接,下一个计数器的输入正确计数, 时钟源是10MHz OCXO,项目的其余部分从十进制计数器获得时钟,以1MHz 运行,尽管低负荷周期似乎正常。

问题可能与计数器的3态输出有关,因为输出似乎缓慢脱落, 我可以为每个班次登记表的输出添加一个和门作为一种变通办法,但我必须订购更多,我无法在项目板上安装更多内容,因此我将在此处发布信息,以查看是否还有其他事情可以做。

您可以看到预期电路如何与 Falstad 电路模拟器配合使用: https://tinyurl.com/y48e6lsl

这些计数器不会在模拟中滚动,因此我可以看到它是否正确输出数据,4个计数器和锁扣使 SN74LV8154计数器成为移动寄存器,然后它们连接到移位寄存器。

我只是模拟前8位计数器以简化计数器,但您可以看到寄存器选择状态。

单击针脚 H 中的串行至少1个时钟周期以触发它

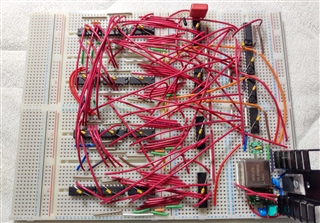

下面是我的项目图片

OCXO 的 SOT-23是一种3.3V 至5V 电平转换器,请查看您是否可以理解其余的电平转换器。

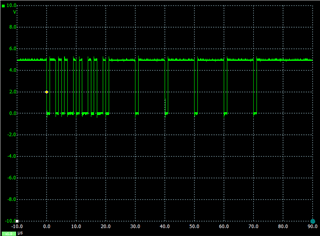

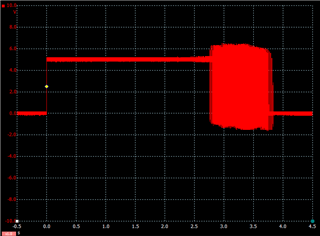

在这里,您可以看到2个输出示例,其中每10微秒是串行停止位,后面是8个数据位,然后是下一个数据字节前的1个时钟暂停,您可以看到这是由于移位寄存器的连接方式 非门,如果再输出1个数据在数据被阻止后仍处于高位。

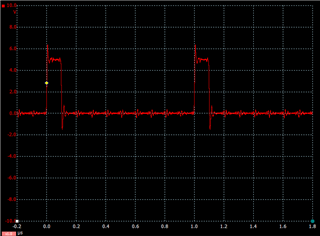

这是串行时钟,过冲主要是由示波器探头接地导线引起的:

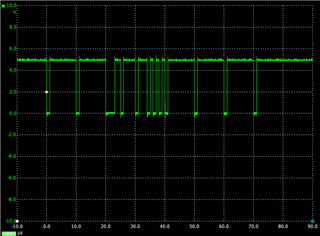

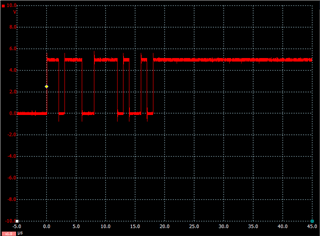

在这里,您可以看到只有当移位寄存器输出 QH 保持在高态时才会发生的振荡,该值大约为37MHz:

在这里,您可以看到与上述相同的 QH 输出,但当串行数据传输时,请记住,当 SH/LD 变低时,它将保持随机状态:

我希望这是足够的数据;)