https://e2e.ti.com/support/logic-group/logic/f/logic-forum/1077065/sn74bct760-spice-model

部件号:SN74BCT760e2e 团队您好!

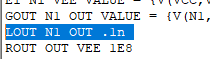

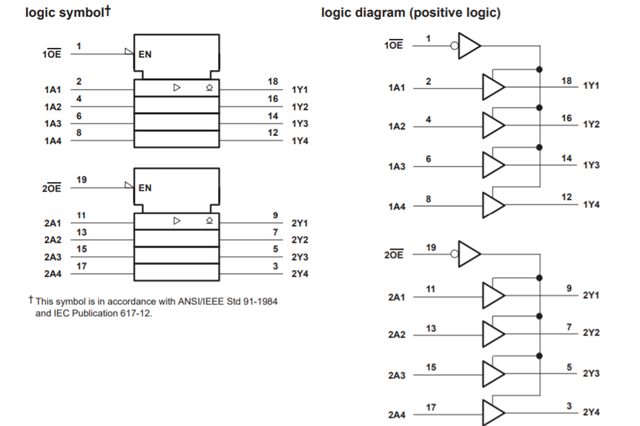

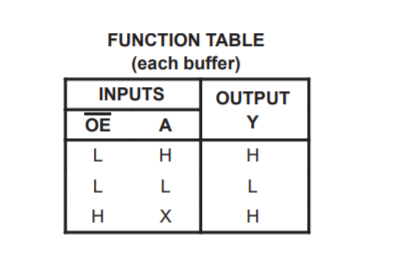

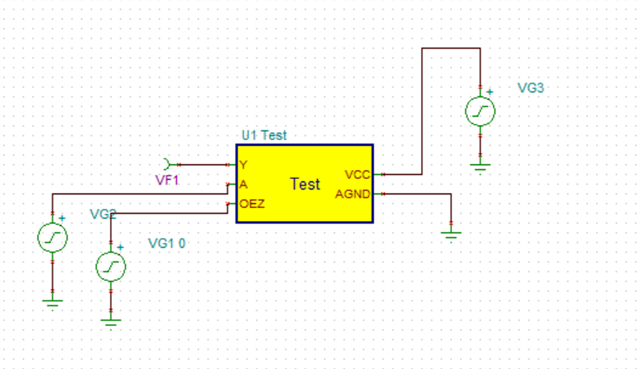

我正在尝试使用 TI.com (https://www.ti.com/lit/zip/scbm122)上提供的 SN74BCT760 Spice 模型运行基本仿真。 理想情况下 ,尝试实施并验证缓冲区逻辑-->

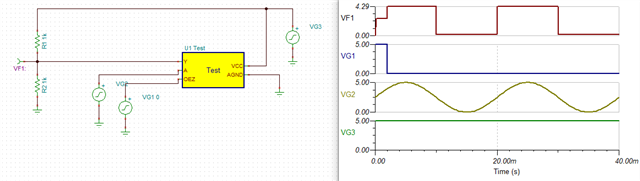

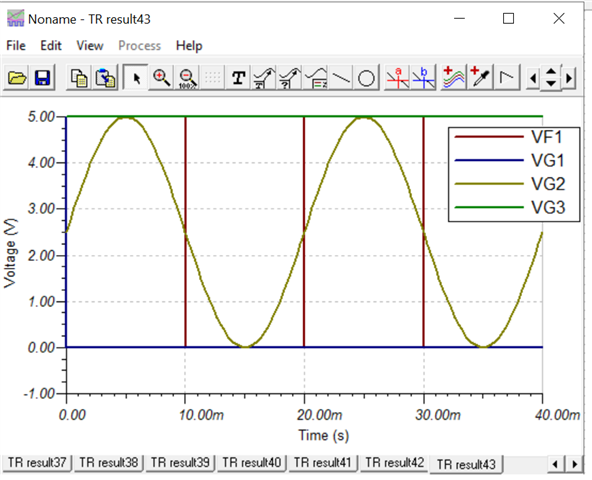

以下是模拟屏幕截图以及瞬态分析-->

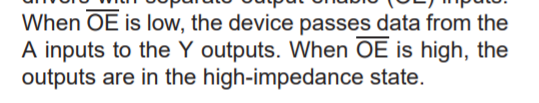

问题在于曲线 VF1 (缓冲器的输出 Y),只要 OE 非 pin 过低,它最好遵循曲线 VG2 (输入)(传递数据而不做正确更改吗?)。

请让我知道我在这里可能缺少的理解。 随函附上了 TINA TI 文件。

谢谢,

阿努布