https://e2e.ti.com/support/logic-group/logic/f/logic-forum/1083149/sn74lvch8t245-sn74lvch8t245

部件号:SN74LVCH8T245“线程”中讨论的其它部件: SN74LX8T245

你(们)好

我使用 SN74LVCH8T245作为从我的 FPGA (1.8V)到我的 CPU (3.3V)的电平转换器

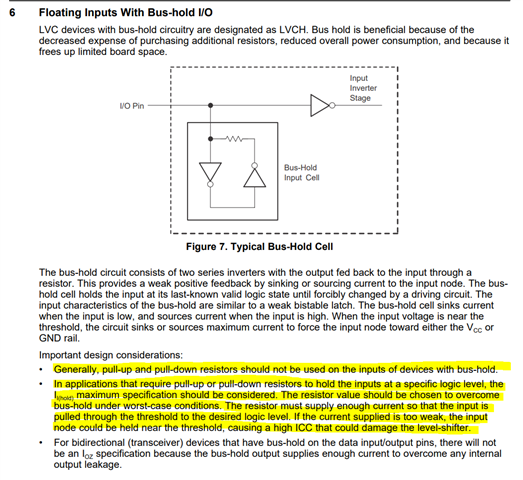

在您编写的数据表中,不建议使用上拉/下拉电阻器

在设备输入上(这也适用于设备输出??)

此请求的原因是什么? 这是因为两者之间会出现一个“分压器”

设备内部电阻器和主板外部上拉/下拉电阻器?

但是,在第10节中,您写道,当针脚保持低位(始终处于活动状态)时,它是

最好使用设备输入上的上拉/下拉... 这是为什么?

什么是底线,是否有外部 PU/ PD?

如果我的 oen 针脚连接到 POR (开机重置)信号(POR 为“1”,持续250毫秒

自通电后,电流一直很低),它 是否仍然符合第10条的规定

我应该将我的输入连接到 PU/PD? 请解释...

谢谢

阿姆诺异构物