我正在TXS0102中进行设计。 数据表指出,VIL必须小于0.15V才能保证VOL符合I2C规范(0.4V)。 遗憾的是,大量部件表明其最大VOL为0.4V,这对于TXS0102来说似乎过高。 我亦明白到,事实上,大部分地区的VOL最终应远低于0.4V。

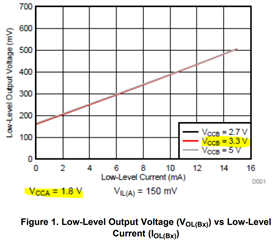

在TXS0102数据表中,我看到此图表:

当我曲线贴合这个时,我会得到类似的东西

容积= 157mV +(23mV/mA)*输出电流

这似乎表明晶体管电阻为23Ω Ω。 此外,该线路的起点为157mV,而不是150mV,这意味着晶体管上的电压降为7mV,这表明通过晶体管的电流为0.3mA。 通过晶体管的电流应该只是通过内部10k上拉的电流。 因此(3300mV-158mV)/10k=0.3mA,这是对线的。

根据这种逻辑,如果我的其中一个设备提供了最坏的情况VOL =0.4V,那么这个芯片将会得到它,因为它是VIL。 如果TXS0102的输入电压为0.4V,我们还假设我有额外的10k上拉电压, 然后,通过晶体管的电流仅为内部上拉电流为0.3mA,外部上拉电流为0.3mA,总共为0.6mA (确实要小一些,因为VIL是0.4V,而不是0.15V,但相差很小),这意味着晶体管中的电压为14mV, 这意味着容积是414mV。

虽然这超出了VOL的I2C规范,但对于由1.8V供电的器件(其VIL为540mV),它仍在VIL规范范围内。

我所描述的内容是否有任何问题? TXS0102是否实际将0.4V识别为低电压? 此外,我是否可以将此逻辑应用于B作为输入,A作为输出?