请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:SN54AC244 您好!

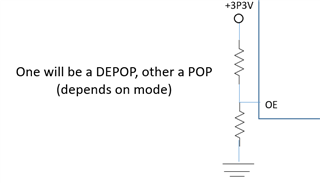

我需要在电路板设计的一种模式下在 OE 上添加一个上拉电阻器、并在设计的另一种模式下在 OE 上添加一个下拉电阻器、这样、一种模式下驱动器不会激活、而在另一种模式下、驱动器将激活。

为此、我将取消选择其中一个电阻器。

我的问题是如何确定这些电阻器的值? 我看到泄漏电流为1uA。 我是否只需选择一个不会改变 OE 输入上 VIH 和 VIL 电平的电阻器?

换句话说、对于下拉、如果我使用1K 下拉电阻、则在输入引脚上只会看到1K * 1uA =.001V、这完全符合 VIL 规格、以确保它保持低电平。

如果我使用1K 上拉电阻、我会在输入引脚上看到1uA * 1K =.001V、3.3 -.001 = 3.299V 的压降、这完全符合 VIH 规格、以确保其保持高电平。

是这样吗?

谢谢、

Matty