大家好、

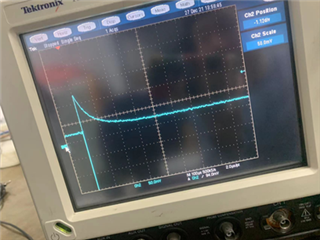

我的客户在执行 BCI 测试时遇到 LED 闪烁问题。

问题描述:

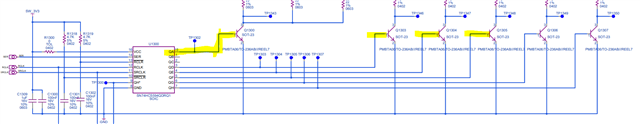

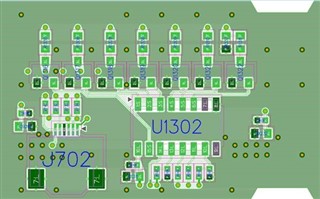

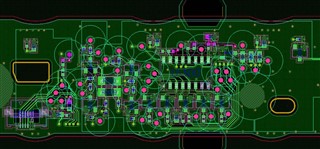

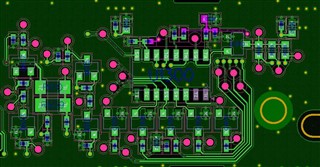

客户将数据加载到 SN74HCS594-Q1中(所有输出均设置为1)、在 BCI 测试期间、我们不会修改任何数据、我们看到 LED 在不同通道上在110Mhz~200MHz 范围内闪烁(这意味着某些 LED 仍亮起、某些 LED 通道熄灭)。 我们测试了2块电路板、这两块电路板都出现了问题。 我们为输入提供所有1 (高电压电平),原理图如下:

e2e.ti.com/.../LED_0030_driver.pdf

您可以观看下面的视频以检查问题现象:

e2e.ti.com/.../1112e3c35e49e6f4aba216081de60cdf.mp4

由于客户的原理图设计处于 EMC 测试过程中、您能不能在今天之前帮您查看客户原理图设计。如果您对调试此问题有任何想法、请立即向我们提供、谢谢。