Other Parts Discussed in Thread: SN74LVC16T245, SN74LVC827A, SN74AUC16244, SN74AUC244, SN74AUCH16244, SN74AUCH244

主题中讨论的其他器件: SN74LVC827A、 SN74AUC16244、 SN74AUC244、 SN74AUCH16244、 SN74AUCH244

我的客户请求将10位从2.5V FPGA 转换为1.8V、

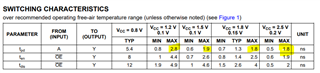

由于 数据速率大于100Mbps、我建议使用 SN74LVC16T245、假设我可以不使用额外的6位。

总共有1个100MHz 时钟位和9个数据位(低于100MHz)

问题包括:

SN74LVC16T245中

假设时钟为100MHz、其他输入是否需要共享余数100Mbps? 还是强制其他位 以100MHz 运行?

2 是否所有输入位都以 最大数据速率变化?

我建议的另一个选择是 SN74LVC827A 10位缓冲器、我将会问同样的问题、此外: SN74LVC827A 在 150MHz 时是否支持2.5V -> 1.8V?