请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

https://e2e.ti.com/support/logic-group/logic/f/logic-forum/1063031/txs0102-i2c

器件型号:TXS0102大家好、

我的客户在其项目中使用 TXS0102、但他们遇到了以下问题、您能不能提供一些建议?

谢谢你。

客户发现 I2C 的 SDA 信号在 txs0102的 B 侧有一个长时间保持低电平的问题。

I2C 接口是一种 OD 门结构、速率为100kHz。

1.客户在 i2c 总线上使用 TXS0102,连接拓扑为:CPU--I2C--- TXS0102 I2C--SPD (EEPROM);

问题是 CPU 端 I2C 在写入 EEPROM 时、shave 在从器件(EEPROM)的 ACK 应答后释放 SDA 信号、但实际测试发现 txs0102的 B2始终处于低电平。 因此、时序没有下一个启动过程、后续时序不时序。

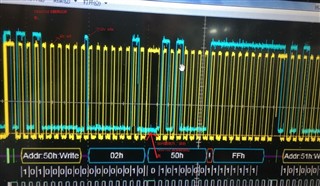

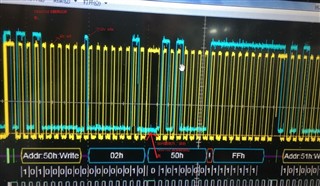

如下面的图1所示、TXS0102 B 侧的测试结果表明、在 EEPROM 使用图1中的箭头释放 i2c 后、i2c_sda 应被拉高、但实际测试波形不会被拉高。 这会导致 i2c 时序缺少启动过程。

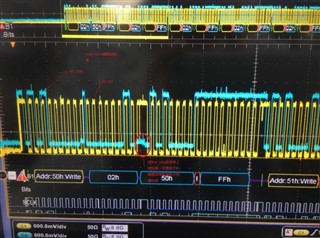

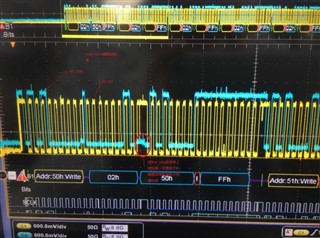

如下面的图2所示、TXS0102 A 侧测试的结果相同、结果是 在 EEPROM 释放 i2c 后、A 侧的 i2c_sda 应通过图2中的箭头被拉高、但实际测试波形未被拉高。 虽然该波形突出、但整个 i2c_sda 电平较低、因为 B2始终拉低。

图1.

图2.

您能否帮助分析为什么 txs0102在 i2c 信号被拉取时表现异常、导致该信号的原因是什么?

非常感谢。

此致、

Ivy