主题中讨论的其他器件: CC2530、 SN74AUP1G06

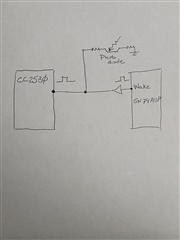

由于缺少 I/O 而不得不发挥创意(CC2530系列)。 使用 OR 门(SN74AUP1G32)将两个外部数据信号带到配置为输入的 CC2530上的 GP/IO。 这一相同的 CC2530 I/O 被定期 用作输出、以便为外部器件提供逻辑1。

当或门输出通常为低电平时(逻辑零- 0.0伏)、将逻辑1 (3.3伏)应用于 SN74AUP1G32或门的输出会产生什么后果? 不同的问题是、当两个输入都为逻辑零(输出为逻辑零)时、返回 OR-Gate 输出的阻抗是多少? 数据表未提供等效电路图。 输出是否为高阻抗?

非常感谢。

Jim