你好

SR 锁存器似乎是唯一不需要 CLK 的触发器。

请帮您确认吗?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

你好

SR 锁存器似乎是唯一不需要 CLK 的触发器。

请帮您确认吗?

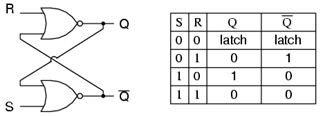

这可能有助于了解 SR 锁存器的使用情况。 如果您的系统需要一个、您可以通过双或非门或双与非门轻松构建它(取决于您是否需要低电平有效输入或高电平有效输入)。 例如、SN74AUP2G02可被用来锁存:

也不会从 https://www.allaboutcircuits.com/textbook/digital/chpt-10/s-r-latch/中锁定图像

-

只要 D 型触发器具有异步预设和清零引脚(或设置/复位... 相同)。

以这种方式使用时、D 和 CLK 输入保持未使用状态(端接至 GND 或 VCC)。

-

还必须注意的是,锁存器没有默认输出状态--您必须在系统启动时强制它们进入所需状态。 [常见问题解答]锁存器件的默认输出是什么? (触发器、锁存器、寄存器)