主题中讨论的其他器件:SN74LXC8T245、 SN74LXC8T245-Q1

大家好、

我的客户观察 到、即使 OE 引脚上拉至 VCC、SN74LVC8T245-Q1在上电期间也会产生高电平脉冲。 但在数据表中、它说"为了确保加电或断电期间的高阻抗状态、OE 应通过一个上拉电阻器连接到 VCC "。 我是否可以知道如何避免这种高电平脉冲? 或者、我们是否有 P2P 器件、例如 在上电期间将保持高阻抗状态的 SN74LXC8T245?

谢谢。

此致、

利维亚

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

大家好、

我的客户观察 到、即使 OE 引脚上拉至 VCC、SN74LVC8T245-Q1在上电期间也会产生高电平脉冲。 但在数据表中、它说"为了确保加电或断电期间的高阻抗状态、OE 应通过一个上拉电阻器连接到 VCC "。 我是否可以知道如何避免这种高电平脉冲? 或者、我们是否有 P2P 器件、例如 在上电期间将保持高阻抗状态的 SN74LXC8T245?

谢谢。

此致、

利维亚

您好!Dylan、

我是否可以问 、与 SN74LVC8T245-Q1相比、SN74LXC8T245内部是否存在可保证 无干扰加电的差异? 如 SN74LVC8T245-Q1数据表中所述、如果我们将 OE 上拉至 VDD、I/O 引脚在上电期间将具有高阻抗。 但客户确实会观察到如下所示的高电平脉冲。

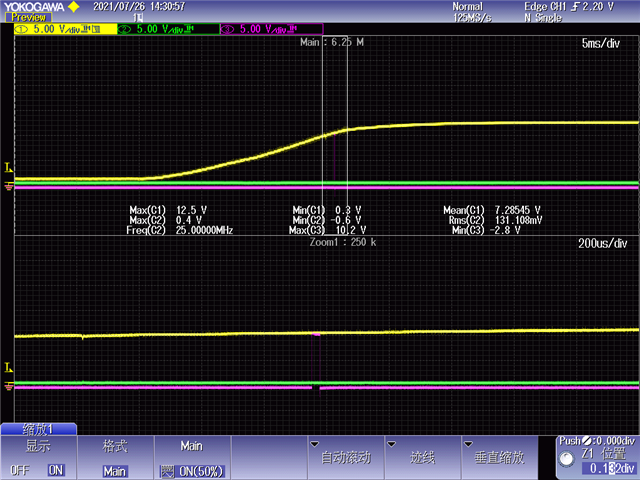

CH1 (黄色)是12V 主电源、通过降压转换为5V、然后通过 LDO 转换为3.3V。 VCCA=3.3V、VCCB=5V、DIR 为 A->B

在客户设计中、5V 电压将首先就绪、 而5V 电压就绪后、SN74LVC8T245-Q1输出(CH3、紫色)处将立即观察到脉冲。 3.3V 准备就绪后、输出将变为低电平。

我要求客户调整加电顺序、如果 VCCA 在 VCCB 之前准备好、则输出端不会有高电平脉冲。 但在客户的设计中、3.3V 是从5V 生成的、因此如果他们需要在 VCCB 之前设置 VCCA、则需要对布局进行更改、而客户不希望这样做... 请帮助您确认更改 SN74LXC8T245是否 可以解决此问题?

谢谢。

此致、

利维亚