https://e2e.ti.com/support/logic-group/logic/f/logic-forum/1016739/vme-9u-board-layout-guidlines

主题中讨论的其他器件:SN74LVC16T245、 SN74LVT16245B大家好、

在我们使用的 Artix7系列 FPGA 设计中、我们正在进行9U 电路板设计。 FPGA 背靠背规划我们有 VME 接口、接口布线长度应约为12英寸。

1) 1) 96引脚连接器至2 英寸电平转换器 、走线具有5.1 @ 50 Ω 阻抗。

2) 2)电平转换器到 FPGA 10英寸布线长度、布线阻抗为5.1 @ 50 Ω。

电平转换器器件型号: SN74LVC16T245 (16位)、SN74LXC8T245QPWRQ1 (8位)。

我们对 VME 接口进行了 SI 仿真。 结果如下所示。

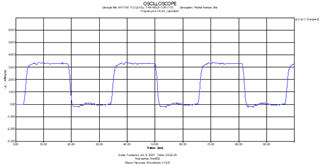

1) FPGA (LVCMOS_3V3_8mA)作为驱动器 LVT (3V3)作为接收器、在时间 信号(传输)质量良好(过冲和下冲在范围内)。

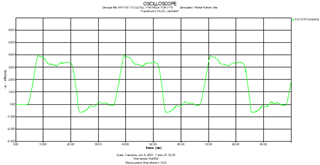

2) LVT (3V3)作为驱动器 FPGA 作为接收器、此时信号 质量不佳。 ( 过冲和下冲在范围内)

列出了问题。

1) 1) LVT 至 FPGA 信号传输线路需要串联端接。 这确实是必需的、还是我们有任何其他方法?

2) 2) VME 接口数据总线是双向总线。 这会将一段时间的 LVT 信号作为驱动器、将一段时间的 FPGA 信号作为驱动器、在这种情况下、我们可以在何处安装串联端接? 或者我们还有其他方法吗?

3) 3)对于数据总线、我们如何使用 OUT 串联端接来控制过冲和下冲?

我们的布线长度为10英寸(最大值) LVT 至 FPGA。 对于我们能够以良好的信号质量实现的这种布线长度、请推荐任何设计方法。

我们的 SI 仿真报告如下所示。 请参阅。

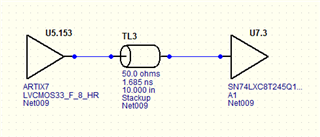

案例1:Artix7至电平转换器

FPGA 器件型号:XC7A200T-1FBG676C

FPGA 缓冲器模型:LVCMOS33_F_8_HR

电平转换器器件型号:SN74LXC8T245QPWR

缓冲器模型:INPUT_3.3V

布线长度:10英寸

布线宽度:5mil

频率:32MHz

- 波形:

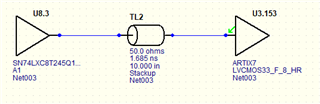

案例3:电平转换器至 Artix-7

FPGA 器件型号:XC7A200T-1FBG676C

FPGA 缓冲器模型:LVCMOS33_F_8_HR

电平转换器器件型号:SN74LXC8T245QPWR

缓冲器模型:INPUT_3.3V

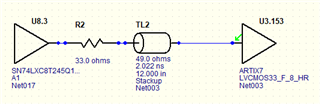

原理图:

布线长度:10英寸;

布线宽度:5mil

频率:32MHz

波形:

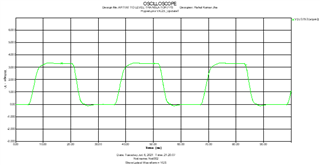

情况4:使用33欧姆串联端接:

到 Artix-7的电平转换器

FPGA 器件型号:XC7A200T-1FBG676C

FPGA 缓冲器模型:LVCMOS33_F_8_HR

电平转换器器件型号:SN74LXC8T245QPWR

缓冲器模型:INPUT_3.3V

原理图:

波形:

此致、

Sivakumar R