主题中讨论的其他器件: 冲击

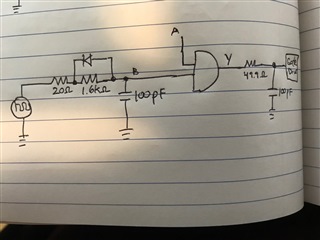

我将配置为双输入与门的 SN74LVC1G57用作死区时间电路的一部分。 请参阅随附的图像以供参考。 VCC 为5V。 使用两个相同的死区时间电路:一个用于高侧开关、另一个用于低侧开关。

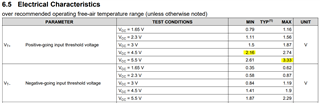

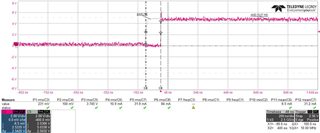

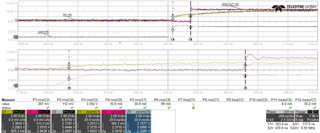

与门的输入 A 始终开启、以实现此分解。 图示的源是400kHz 的方波。 死区时间是通过 RC 常数仅减慢上升沿而产生的。 由于二极管、下降沿不受影响。 我期望死区时间~105ns、因为这是栅极输入 B 达到~2.4V 所需的时间、我近似为正向输入阈值电压(VT+)。 但是、我测量的死区时间为70ns。 我对 VT+的理解是否不正确? Vcc = 5V 时的 VT+是什么? 什么可能导致死区时间为70ns 而不是105ns?