主题中讨论的其他器件:TMS320F280025、 SN74LV4046A

我们需要将电网频率乘以32次才能馈送到 TMS320F280025微控制器中。 我们希望 PLL 能够锁定47Hz 至63Hz 的电网频率。 应用电路如下所示:

R2、R1和 C1的计算如下:

R1选择为100 k 欧姆、电源电压为5 VDC。

Fmin = 47 * 32 = 1502Hz。

从上图中可以看出、C1的值大约为10、000pF。

FMAX= 63*32= 2016 => Fmax/Fmin = 2016/1502= 1.34。

从下图 R2/R1=0.3。 =>R1=100K/0.3= 330K。

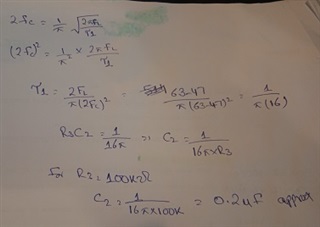

滤波器组件 R3和 C2分别被选为100k 欧姆和0.2uF、如下所示:

我正在使用信号发生器测试电路。 它能够锁定在50至61Hz 之间、但不能锁定在47至50Hz 范围内。 它也不在61Hz 至63Hz 范围内锁定。 如果有人能够验证计算结果并在固定频率捕获和锁定范围时提供一些指导、那将是不错的。