常见问题解答:逻辑和电压转换 > 电源和热性能>>电流常见问题解答

简而言之-对于 SN74LVC1G08等单电源逻辑器件、使用0.1uF 电容;对于具有多个电源引脚的器件(例如 SN74LVC16244A (具有4个电源引脚)的每个电源引脚、使用0.022uF 电容。

为什么我们根本需要旁路电容器?

旁路电容器的用途是提供一个具有极低阻抗的本地电荷电源、该电荷可由组件快速获得电源。

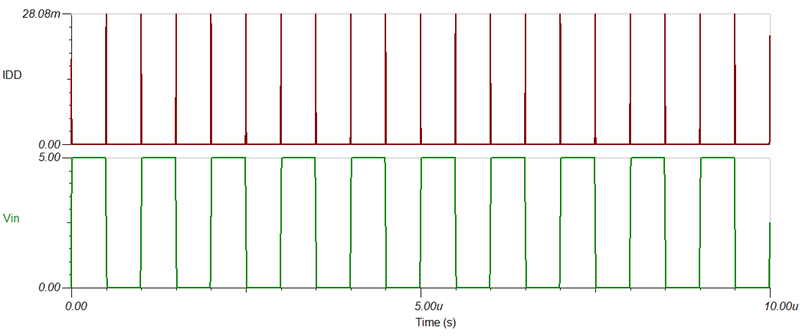

CMOS 逻辑器件在开关事件期间需要比静态运行时消耗更多的功率、这意味着它们必须从电源快速汲取功率。 以下是输入开关事件(仿真)期间来自简单 CMOS 反相器的预期电流图:

如您所见、每次输入转换时都会出现短暂而剧烈的功率尖峰。 由于这些电流尖峰的持续时间非常短且值相对较大、因此具有本地电荷源对于提供稳定可靠的运行至关重要。 通常、电源与逻辑器件的电气距离较远、这会导致电源与器件电源引脚之间的电感和电阻相对较大。

此外、这些尖峰会导致同一电源网络上其他器件的电源干扰。 我们需要防止这种情况、因此添加了旁路电容器。

电容器放置

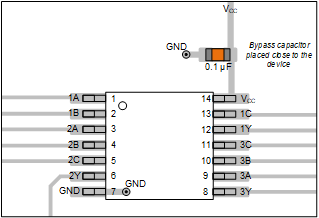

从电气角度而言、旁路电容器应始终尽可能靠近器件放置。 这意味着您需要较宽、较短的布线、并使电容器在物理上靠近器件。 如果需要、可以将其放置在电路板的另一侧以减小距离。

通常、最好将电容器放置在靠近电源引脚的位置、并通过过孔将另一侧连接到接地层、然后也向器件的接地引脚提供过孔。 还有其他可行的方法、但这是最常见且最容易实现的方法。

旁路电容器放置示例。

选择合适的电容器值

必须了解电容器是包含非理想行为的真实元件。 这是实际电容器的常用模型:

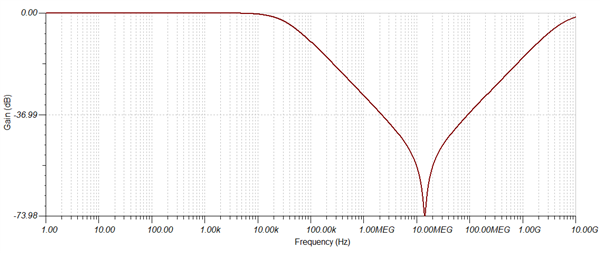

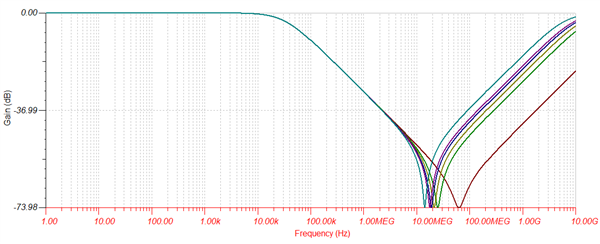

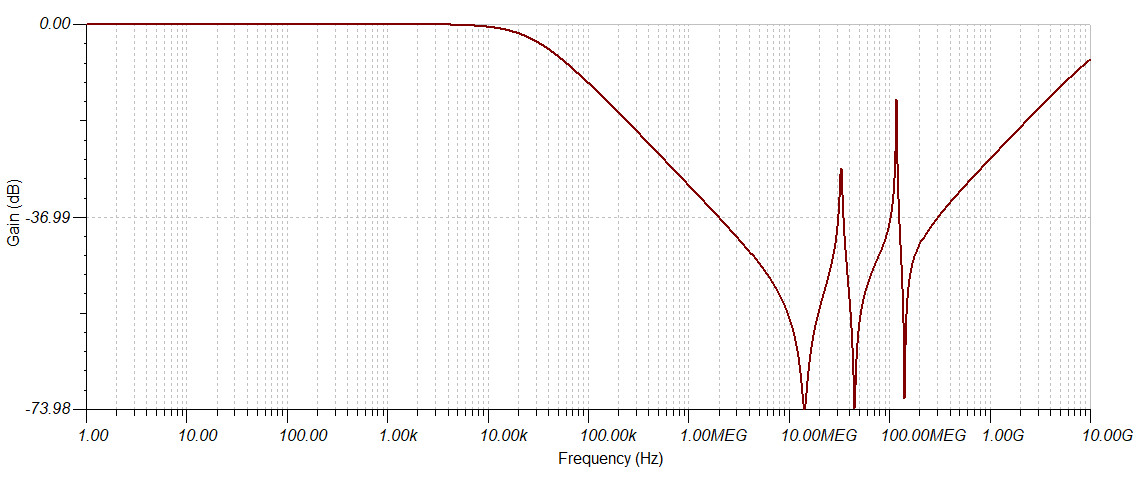

尤其重要的是封装电感。 回想一下电感器的基础知识、它们在较高频率下表现为开路。 这意味着电容器将对其可响应的频率范围有一个上限。 下面是一个电容器的频率响应图、该图使用标准 SMD 封装(1206)中0.1uF 电容器的典型值。

*注意:这不是特定电容器的图、而是模拟响应、以大致显示电容器的响应方式。

上图是对数刻度上的增益与频率间的关系(通常称为波特图)。该电容器的可用带宽范围为大约100kHz 到大约1GHz (图中的"V")。 在最低点、电容器具有最低阻抗、这也是 它提供最大电流的频率(即最快和最佳响应)。 在这种情况下、电容器在10MHz 以上提供最佳性能。

*注意:此处绘制的频率为纯正弦、与逻辑信号的边沿速率直接相关-与信号的数据速率或时钟频率无关。

-

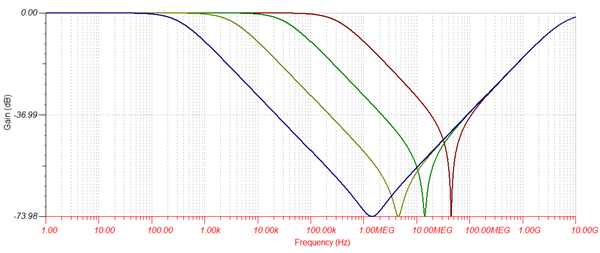

通过改变电容并使其他方面保持恒定、我们可以看到电容值如何影响响应频率:

随着电容器值的增加、低侧的截止频率会降低、而高侧的截止频率保持恒定。 这是因为封装电感保持恒定、而只有电容发生变化。

-

如果我们改变电感、而不是通过更改封装、我们可以看到相反的效果:

通过使用更小的封装(或针对此应用进行优化的封装)来降低电感将增加图高端上的转角频率、而较低的频率将保持恒定、因为电容值保持恒定。

那么、如何为我的应用选择最佳电容器?

*我不打算详细介绍特定封装和类型的电容器性能-考虑到我在 TI 工作、我们不生产电容器、我认为这是一个更适合电容器制造商的讨论。 如果您对该主题的详细信息感兴趣、可以在网站上找到多个应用手册和文章、这些文章详细介绍了这方面的内容、并且非常有趣、内容丰富。 我不会链接其中的任何一个,因为我不想看起来推荐一个特定的制造商--抱歉。 Google 是一个很好的资源,你可以从搜索“选择一个旁路电容器”开始。

在特定应用中、选择最佳旁路电容值的主要标准有两个:

预期的信号频率分量

2.预期负载-包括同时开关的通道数

(1)对于第一个标准、我们必须查看信号的频谱。 我不打算详细介绍这方面的内容、但假设理想逻辑信号(方波)具有无限的频率分量、但实际信号的频率分量有限(有关详细信息、请搜索"理想方波带宽")。 这些主要由信号的边沿速率控制-通常而言、逻辑器件产生的信号具有高达约300MHz 的主要频率分量。 请不要将其与工作频率混淆--您可以有一个1kHz 信号,它具有300MHz 的频率分量,因为边沿非常快。

为了确保您能够根据需要快速提供电流、电容器的带宽应包括在所需的最大频率下尽可能低的阻抗。 一般来说、0.1uF 电容器将覆盖~15kHz 至>1GHz 的广泛频率范围、但您可以从上面的图中看到、它没有针对300MHz 带宽信号进行优化。 您可以添加具有较小值的额外并联电容器以覆盖较高的频率范围。 下面是使用三个并联电容的示例、电容值分别为0.1uF、0.01uF 和1000pF:

(2)对于第二个标准、我们将专门研究输出的每个开关从电容器中汲取的电荷量。

在电荷共享的背景下,你可以考虑这一点--如果你的逻辑栅极上有一个0.1uF 的容性负载,并且你的电源有一个0.1uF 的电荷源(没有其他电源), 然后、您预计输出端的电源电荷恰好是电荷的一半、因此输出端的电压将被削减一半、而在此过程中、您的电源电容器上的电荷将被使用一半。

当然、逻辑门的典型输出负载应该更像10pF、因此在典型系统中、电荷共享会有很大不同。 使用10pF 电容器和0.1uF 旁路电容器时、共享的电荷将导致输出端的 Vcc 达到99.99%。

您不希望仅使用10pF 电容器绕过逻辑门的电源、因为这将无法为输出提供足够的电荷。 一个良好的经验法则是、使您的电源电容器至少比您的输出负载大一个数量级。 同样、0.1uF 电容器很容易满足此标准、因此对于旁路电容器而言、它是一个很好的通用选择。