主题中讨论的其他器件: SN74LVTH125

您好的支持团队。

我收到了客户提出的以下一些问题。

这是否意味着不推荐为输入(A)和输出(Y)使用下拉/上拉电阻器?

2.如果我在输入或输出端使用上拉/下拉电阻器、是否会产生不良影响?

3.如果我在输入和输出悬空的情况下启动电源、输出是否会保持在 L?

4.了解以下情况是否正确:如果电源接通时输入源变为高阻态、则当您希望为输出获取 H 时、输入需要一个上拉电阻器?

您能就上述问题告诉我吗?

此致、

千兆

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好的支持团队。

我收到了客户提出的以下一些问题。

这是否意味着不推荐为输入(A)和输出(Y)使用下拉/上拉电阻器?

2.如果我在输入或输出端使用上拉/下拉电阻器、是否会产生不良影响?

3.如果我在输入和输出悬空的情况下启动电源、输出是否会保持在 L?

4.了解以下情况是否正确:如果电源接通时输入源变为高阻态、则当您希望为输出获取 H 时、输入需要一个上拉电阻器?

您能就上述问题告诉我吗?

此致、

千兆

输入绝不能悬空(请 参阅[常见问题解答]慢速或浮点输入如何影响 CMOS 器件?)。 如果 在上电期间未驱动输入、则需要一个上拉或下拉电阻器。

至于输出、SN74LVT125本身不会影响上拉或下拉。 如果您的电路即使 在 SN74LVT125 断电或禁用时也需要有效信号、则需要该信号。

您好、Higa、

[引用 userid="421485" URL"~/support/logic/f/logic-forum/989144/sn74lvt125-behavior-with-hi-z-input-at-startup/3655122 #3655122]SN74LVT125具有总线保持功能、但输入是否仍然需要上拉或下拉电阻器? (我的问题是有关启动的。)请查看此应用手册的第6.3节 :https://www.ti.com/lit/an/scla015b/scla015b.pdf

谢谢!

乍得克罗斯比

您好、Crosby–San

感谢你的答复。

>输入绝不能悬空(请参阅 [常见问题解答]慢速或浮点输入如何影响 CMOS 器件?)。 如果 在上电期间未驱动输入、则需要一个上拉或下拉电阻器。

当 Ladisch-San 第一次回答时,不应该让输入悬空,这是不对的?

下拉时电阻值的计算公式是否正确?

Rd = VT/IIhold (最大值)

我无法从数据表中找到 VT 和 II (HOLD)最大值。 VT = 1.5V? II (保持)最大值= 75uA?

此致、

千兆

您好、Higa、

如果您的应用需要总线保持功能、我建议您使用 SN74LVTH125 -这个肯定具有总线保持功能。 我将亲自测试 SN74LVT125、以验证它是否具有总线保持功能。

[引用 userid="421485" URL"~/support/logic/f/logic-forum/989144/sn74lvt125-behavior-with-hi-z-input-at-startup/3655325 #3655325"]当 Ladisc-San 首次回答时,是否不应使输入悬空?我仍然建议在不由另一个器件驱动的信号线上设置一个上拉电阻。 总线保持电路旨在缓解这种情况;但是、总线保持器件上具有大小正确的上拉电阻器不会对其造成损害。

[引用 userid="421485" URL"~/support/logic/f/logic-forum/989144/sn74lvt125-behavior-with-hi-z-input-at-startup/3655325 #3655325"]下拉时电阻值的计算公式是否正确?

Rd = VT/IIhold (最大值)

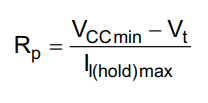

[/报价]我建议使用前面链接的应用手册中的 Rp 计算:

SN74LVTH125的数据表具有 II (HOLD)规格:

我们没有在数据表中定义 VT、因为实际阈值电压会根据温度、晶圆批次和其他因素的整个转换而变化-但-设置 VT = 1/2 * VCC 通常是一个安全的选择。

谢谢!

乍得克罗斯比

大家好、 Daisuke Higa、 Clemens Ladisch、

我完成了对这两个器件(SN74LVT125和 SN74LVTH125)的测试、并且两个数据表都正确-这些器件在输入上都具有总线保持功能。

希望这能帮助您实现千兆。

谢谢!

乍得克罗斯比