请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:SN74LV165A 团队、

我的客户对 VCC=3.3V 时的时序要求有疑问。

请提供以下方面的更多详细信息:

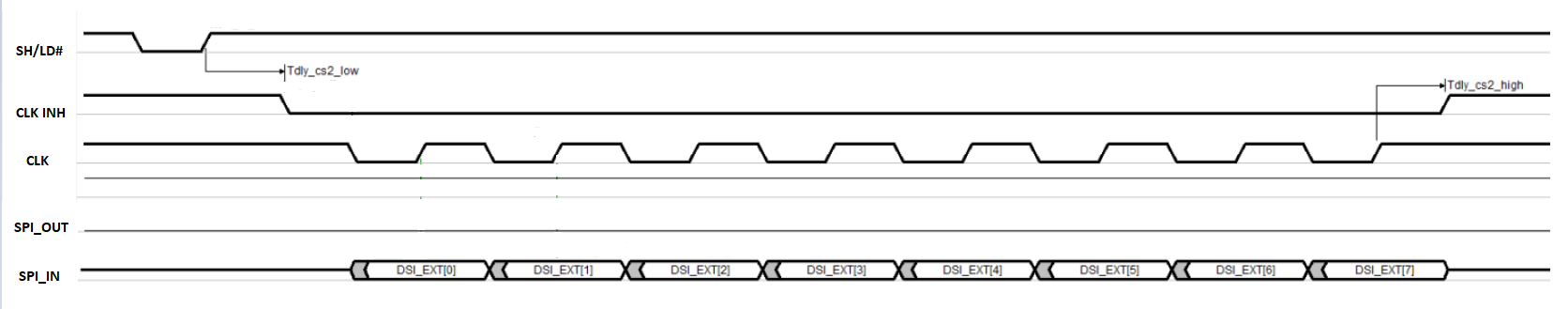

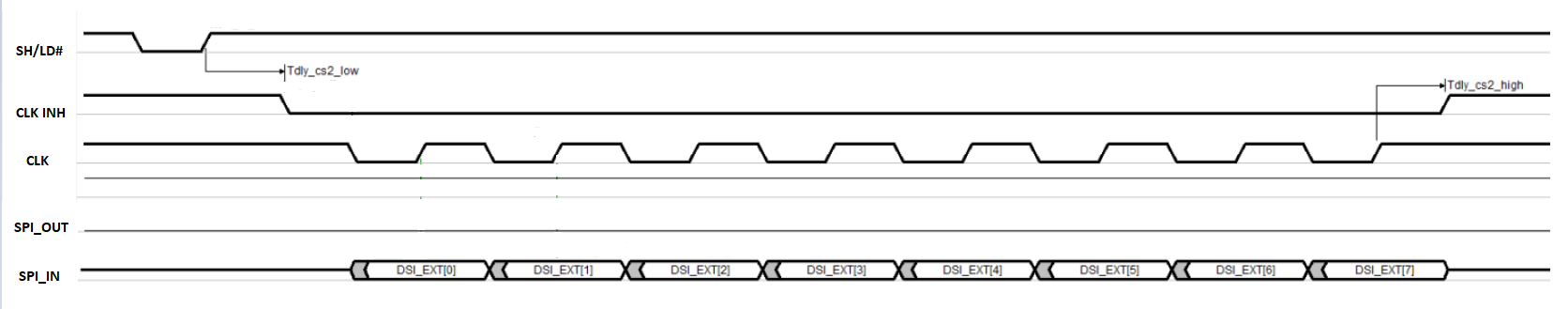

- SH/LD#上升沿(TDLY_CS2_LOW)产生的最小 CLK INH 输出延迟

- 在时钟的最后一个下降沿(TDLY_CS2_HIGH)之后 CLK INH 输出的最小启用延迟

谢谢、致以诚挚的问候

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

团队、

我的客户对 VCC=3.3V 时的时序要求有疑问。

请提供以下方面的更多详细信息:

谢谢、致以诚挚的问候

您好!

我不确定我是否完全理解您在这里提出的问题。

[引用 userid="71087" URL"~/support/logic/f/logic-forum/984168/sn74lv165a-timing-details-with-vcc-3-3v "] SH/LD#上升沿(TDLY_CS2_LOW)产生的最小 CLK INH 输出延迟[/quot]CLK INH 和 SH/¯L¯D¯均为输入。 数据表中指定的 SH/¯L¯D¯变为高电平与 CLK INH 变为低电平之间没有最短时间、因此这可以同时发生。

[引用 userid="71087" URL"~/support/logic/f/logic-forum/984168/sn74lv165a-timing-details-with-vcc-3-3v "]由于 CLK 和 CLK INH 引脚是可互换的、因此在 CLK 保持高电平后、CLK INH 上升的方式是可以的。 您可以假设数据表第6.7节中标记为 CLK INH 的设置时间参数在 CLK↑之前 也适用于这种情况。

谢谢!

乍得克罗斯比