Other Parts Discussed in Thread: SN74HCS594, SN74LVC1G04

主题中讨论的其他器件: SN74LVC1G04

尊敬的 TI 专家:

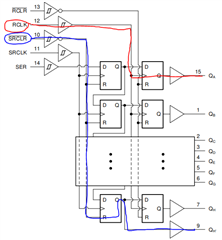

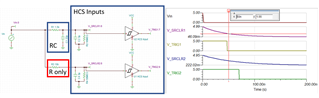

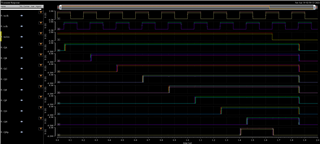

我们希望使用一个 SN74HCS594器件链作为通过 SPI 控制的 IO 扩展器。 并行输出寄存器(链中所有器件的)的时钟将连接到!CS 信号。 在!CS 为高电平时(例如使用逆变器)通过!SRCLR 清除移位寄存器,以便在重新开始通信时具有已定义的移位寄存器内容,这将非常方便。

在 RCLK 的上升沿之后是否有一个时序要求、直到移位寄存器被!SRCLR 清零、这样(未清零)移位寄存器的内容被存储在输出寄存器中?

我知道"!SRCLR 在 RCLK↑前处于低电平"设置时间规格、但我认为这是将清除的移位寄存器内容复制到输出寄存器所需的时间、因此所有输出都为低电平。 对吧?