主题中讨论的其他器件: SN74HCS74

你(们)好

我想知道 SN74LVC2G74-Q1对高/低输入电平进行采样的时序是什么?

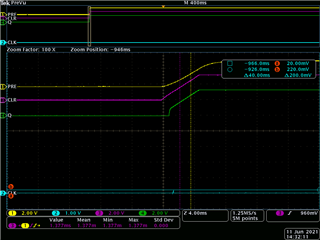

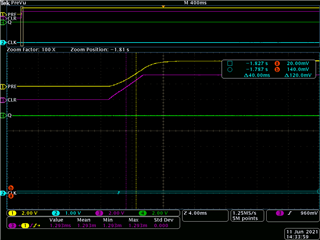

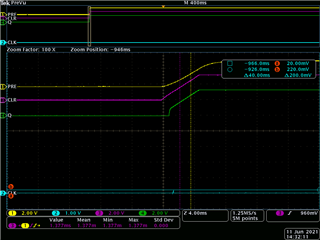

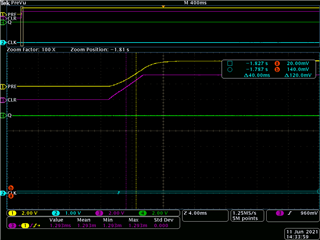

在下面的情况下、Vcc、D 和 CLR 连接到 Vcc。 PRE 引脚通过 RC 延迟连接到 Vcc。

我发现 Q 正在输出、因为 Vcc 尚未准备好。 这是正常性能吗?

我发现在重新启动时、Q 有时未输出。

毕竟、我想知道以下2个问题。

1.输入的采样时序是多少?

2.引导设备时,我想使 Q 输出高电平而不使用 CLK 输入,如何使其稳定?

谢谢!!!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

你(们)好

我想知道 SN74LVC2G74-Q1对高/低输入电平进行采样的时序是什么?

在下面的情况下、Vcc、D 和 CLR 连接到 Vcc。 PRE 引脚通过 RC 延迟连接到 Vcc。

我发现 Q 正在输出、因为 Vcc 尚未准备好。 这是正常性能吗?

我发现在重新启动时、Q 有时未输出。

毕竟、我想知道以下2个问题。

1.输入的采样时序是多少?

2.引导设备时,我想使 Q 输出高电平而不使用 CLK 输入,如何使其稳定?

谢谢!!!

嗨、Deshawk、

可以在数据表的第5页找到时序要求。

但是、当您引导器件时、输出将未知、因此很可能在引导期间有时会将 Q 输出设置为高电平、有时会将 Q 输出设置为低电平。

请参阅此常见问题解答

[常见问题解答]锁存器件的默认输出是什么? (触发器、锁存器、寄存器)

施密特触发器输入可在输入端为您提供已知状态。 SN74HCS74等器件内置了这些功能。

谢谢、

Rami