你(们)好

当进行级联连接 SN74HC595时 、段器件在某些位中有一些随机错误。 我怀疑 QH'和 SRCLK,

第9个 ScrLk 的上升沿会将 QH'引脚值(@第8个 ScrLk)发送到第二部分 SER 引脚、同时会更新 第一个 sn74hc595

QH'引脚值。 如果 QH'更新早于 QH'发送到第二部分 SER 输入、则第二部分将出错。

我理解正确吗? QH'下降沿是否晚于第9个 SRCLK 上升沿? 我是否有任何方法或提示来进行测量和测试、以便更清楚地显示哪个参数?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

你(们)好

当进行级联连接 SN74HC595时 、段器件在某些位中有一些随机错误。 我怀疑 QH'和 SRCLK,

第9个 ScrLk 的上升沿会将 QH'引脚值(@第8个 ScrLk)发送到第二部分 SER 引脚、同时会更新 第一个 sn74hc595

QH'引脚值。 如果 QH'更新早于 QH'发送到第二部分 SER 输入、则第二部分将出错。

我理解正确吗? QH'下降沿是否晚于第9个 SRCLK 上升沿? 我是否有任何方法或提示来进行测量和测试、以便更清楚地显示哪个参数?

感谢您提供原理图、

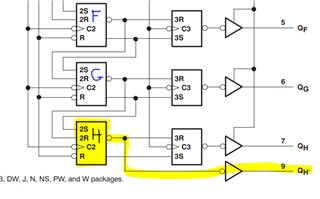

QH'是内部移位寄存器 H 的直接输出、如数据表中的方框图所示:

当级联器件时、最好同时为所有器件计时。 如果这是不可能的(即时钟和两个器件物理分离)、则应首先对链中的最后一个器件(U4)计时、以防止出现错误。 这使得最后一个器件能够首先加载到所有寄存器中(包括第一个器件的输出)、然后新数据被加载到第一个器件中。

我在这里看不到您的连接有任何问题。 最可能的问题是 U3和 U4 SRCLK 触发之间的延迟。 如果两个器件的物理隔离距离很远、则可能会导致数据出错。 相对较重的容性负载也会导致问题。

另一个常见的错误来源是 SRCLK 输入上的缓慢输入转换--您能获得两个器件的时钟输入的示波器截图吗? 最好在100ns/div 刻度或更小的刻度上