主题中讨论的其他器件:SN74LVC1G125、

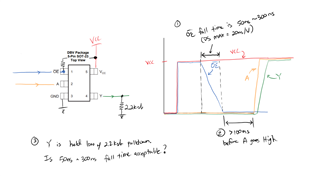

在下面、我附加了 SN74AUC1G125和 SN74LVC1G125用例的图像。

Δv 而言、数据表中的 Δt μ V/μ s 状态在 VCC = 1.5V 时为20ns (最大值)、在 VCC = 1.8V 时为10ns (最大值)。

1)这也适用于 xOE、对吧?

2) 2)如果将 xOE 变为低电平并激活器件的下降时间过长(50ns~300ns)、则输出可能会在高阻态和驱动之间来回翻转、对吧?

3) 3)在上面的#2中、如果 A 为低电平、并且 Y 通过2.2kΩ Ω 电阻器拉低、直到 xOE 拉低100ms 时该怎么办?

在这种情况下、即使输出在高阻态和被驱动之间来回翻转、它仍然是低电平、对吧?

这是否违反了 Δt μ V/μ s 的 Δv 限制-因为输出只能在 xOE 下降转换期间为低电平?