我想知道、如果 VCCA 受电、EN 处于活动状态(保持低电平)、转换 DIR 来自 A 到 B、但 VCCB 未受电、则主题器件会发生什么情况。

从 VCCA 电源轨到 VCCB 电源轨是否存在任何泄漏电流/电压?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

我想知道、如果 VCCA 受电、EN 处于活动状态(保持低电平)、转换 DIR 来自 A 到 B、但 VCCB 未受电、则主题器件会发生什么情况。

从 VCCA 电源轨到 VCCB 电源轨是否存在任何泄漏电流/电压?

嗨、Michael、

在重新阅读问题后、我认为我可能回答了这里的错误问题。 抱歉!

上面我列出了 I/O 引脚的泄漏,这将与 OE 引脚的状态无关,因为 Vcc 隔离功能已经禁用了 I/O。

现在、看看您的实际问题是什么样子的。

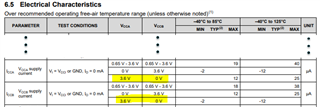

尽管您实际上可能会问 VCCB 断电且/OE 引脚保持低电平时、VCCA 和 VCCB 电源引脚的泄漏电流。 数据表中的 ICCA 和 ICCB 规范中介绍了这一点:

您将看到、输入电压(包括 OE 引脚)指定为 VCCI (与输入端口关联的 VCC)或 GND。

很抱歉、我希望这能清除问题、

Rami Mooti

嗨、Michael、

然后、我会将您恢复到第一个图像。

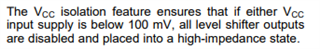

因此、Vcca 在您的条件下为0V、尽管它通常为1.8V、但它会断电、因此暂时为0。 在这种情况下、器件将进入 Vcc 隔离、从而有效隔离总线。 从数据表中:

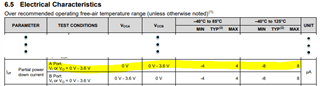

由于这种情况已经隔离了总线并将其置于高阻抗状态、/OE 引脚的状态对通过 I/O 引脚的泄漏没有影响。 拉高时/OE 引脚将使器件进入高阻抗状态、与 拉低时的状态相同、不会覆盖 Vcc 隔离。 请注意、在数据表中、高阻抗状态输出电流 IOZ 具有与部分断电电流相同的规格。

在数据表(上图)中、当满足 VCC 隔离条件(任一电源低于100mV)时、此部分断电电流的参数定义为 Ioff。

VCCB 将为3.3V、包含在指定的0-3.6V 范围内。

只要 I/O 电压保持在0-3.6V 之间、您最坏的情况下将看到数据表中的片段中上述温度条件下列出的泄漏电流。

谢谢、

Rami