主题中讨论的其他器件:LSF0204、 SN74AXC4T774、 SN74AXC2T245

您好!

我们在此设计中使用 LSF0204QPWRQ1。 我们对设计几乎没有什么疑问。

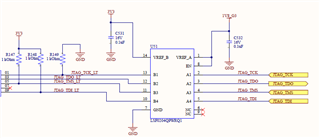

1)原理图1:

LSF0204用于将 JTAG 线路从3V3转换为1V8、反之亦然。

1)根据 JTAG 建议、我们已经为 JTAG TMS 和 TDI 提供了1k Ω。 该上拉电阻是否会对电平转换器的运行产生任何影响? 方向为1V8到3V3。

2)我们是否需要为1V8侧的 JTAG TDO 提供上拉电阻(泄漏电流大于1uA、TDO 方向从3V3变为1V8)?

3)对于 TCK、根据建议使用下拉电阻。 但我们相信,TCK 将始终处于低电平。 TCK 从1V8流向3V3。 当1V8侧的 TCK 输出高电平时、导通晶体管将关闭。 因此、3V3侧的 TCK 将被拉低。 当1V8的 TCK 输出为低电平时、导通晶体管将打开、3V3侧的 TCK 将为低电平。 此分析是否正确?为使 TCK 能够完美地传输、可以对此应用做些什么?

4)如果由推挽驱动、接收器是否需要上拉电阻器?

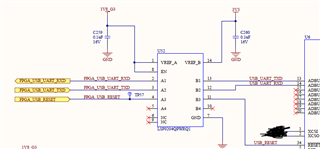

2)原理图2:

1) FPGA_USB_UART_RXD 是否需要上拉电阻器? 它从3V3驱动到1V8

2) UART_USB_RXD 是否需要上拉电阻器? 它从1V8驱动到3V3

3)在 FPGA_USB_RESET 网络(3V3侧)上提供值为10千欧的下拉电阻器。 复位从1V8驱动至3V3。 以下分析是否正确?

当1V8侧处于高阻抗状态(推挽)时、 FPGA_USB_RESET 被下拉、这将打开导通 MOSFET、低电压将在3V3侧提供。 当1V8侧输出高电平时、1V8侧的电压将会高、从而导致 MOSFET 关闭。 3V3侧将悬空、复位信号将处于未知状态。 那么、USB_RESET 网络是否需要上拉?如果上拉大小合适、我们能否在1V8为低电平时将3V3侧驱动为低电平、在1V8为高电平时将3V3侧驱动为高电平(注意:1V8侧将出现下拉电阻)?

4) AX/Bx 的阈值输入电压是多少?导通 MOSFET 将在该电压下关断?

请提供您的答案

谢谢

Viswa