主题中讨论的其他器件: SN74AUP1G14、 TINA-TI

您好!

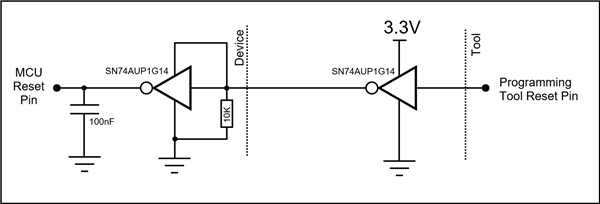

在正常运行期间、我的 MCU 的复位引脚被拉至高电平(3.3V)。 我的系统只有一个连接器、我必须在正常使用中使用该连接器、并在工厂中用于与编程工具连接。

复位引脚被细分为固件闪存所需的多用途连接器。 它不在正常使用中使用。 但是、连接器接口本身有一个要求、这意味着在正常使用期间、这个引脚的有效电压不得超过1V。

因此、我添加了一个逆变器、以便该逻辑电平在连接器侧通常变为低电平。 在正常使用期间、连接器上的电压电平现在为高阻态(允许将 MCU 上的电压电平拉高)、并且在工厂固件闪存期间、连接器上的电压电平被上拉至3.3V (从而在 MCU 上产生一个低复位脉冲)。

此外、该应用要求在正常使用期间具有极低的静态电流消耗。 经过简单搜索、 SN74AUP1G06似乎是一个合理的选择。

我想、最大限度地减小该器件静态电流消耗的一种好方法是通过复位脉冲本身为该逆变器供电。 因此、在正常使用期间、VCC 为高阻态、并且静态电流漏极被限制为流经输出引脚到接地的"Ioff"流。 在编程期间、3.3V 复位脉冲也会在需要的短时间内为逆变器供电。

这是否起作用? 我可以想象的一些问题是:

- 编程脉冲显然必须能够驱动几 mA 的电流为逆变器供电、这可能会导致相当慢的开关打开-可能导致未定义的瞬态行为?

- 我可能应该注意确保 VCC 和逆变器输入之间有一条低电阻路径、以避免上电期间 VCC 低于输入的瞬态周期。

- 为了最大程度地减小"Ioff"、是否最好将 VCC 保持为高阻态? 还是使用10K 下拉至接地?

最后、需要在2030年之前提供器件。 我注意到、数据表的版权为2004年。 因此、如果由于可能的长期可用性或其他原因而对该器件选择存在疑虑、建议用于新设计的替代器件的任何建议都将非常受欢迎。

我们将提前感谢您提供的任何帮助。

此致、

Edward