Other Parts Discussed in Thread: SN74AVC16244, SN74AUC16244

请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:SN74AVC16244 主题中讨论的其他器件: SN74AUC16244

大家好、

您能否帮助确认此设计是否可行? 谢谢!

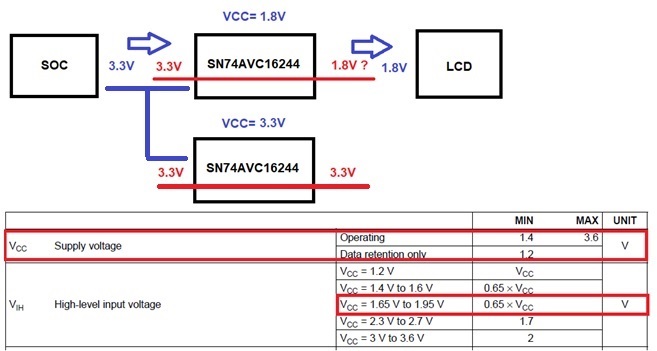

当前的 SOC I/O 为3.3V、需要提供给两个器件、

LCD I/O 为1.8V、另一个 I/O 为3.3V (如下图所示)

如果我们使用 VCC = 1.8V 和3.3V I/O 输入的 SN74AVC16244、我们是否会获得1.8V 逻辑输出?

此致、

Sam Ting