主题中讨论的其他器件: SN74AUP1G98、 SN74HCS00、 SN74LVC2G132

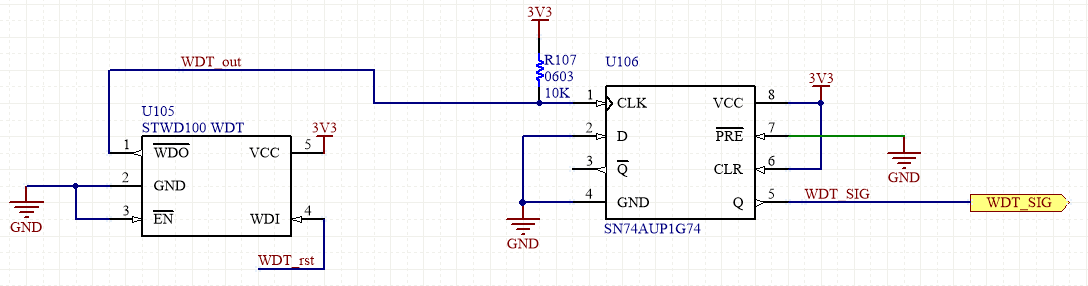

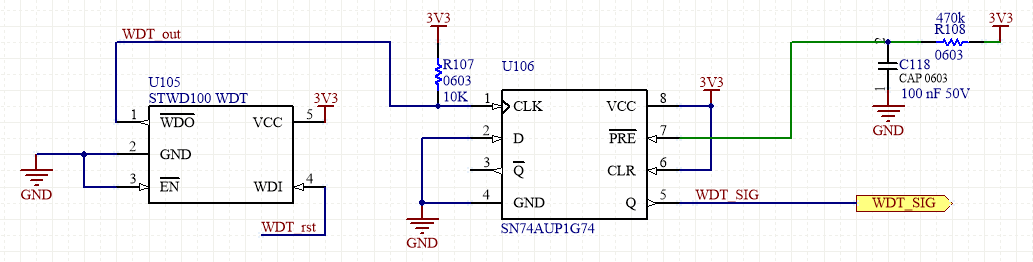

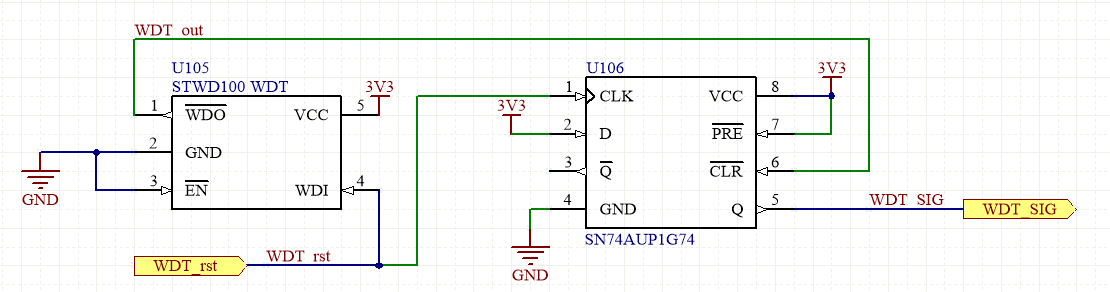

大家好、我打算使用 SN74AUP1G74制作一个经修改的 WDT 电路、以便在 WDT 超时事件之后将 WDT 输出信号保持在低电平。

大多数 WDT 专用电路在 WDT 事件后实现脉动输出、但在我的应用中、我需要一个稳定在0V 的逻辑信号(WDT_SIG 上的0V 将一直运行一个风扇、直到人工干预)。

因此、在开始时、我们需要 在 SN74AUP1G74输出上使用逻辑1 (因此/PRE 引脚连接到 GND)、并且仅在 WDT 超时后、WDT 脉冲才会触发触发触发器的时钟以输出所需的0V 输出

我的问题是、在上电期间、CLK 上的上升信号可能被视为时钟转换、数据被锁存到输出。 我知道这个组件专门针对这个情况有一个预设引脚、但是我找不到针对这个情况的任何特定时序信息:在触发器上的有效 VCC 之前、CLK 引脚的变化需要多长时间被认为是一个"有效边沿转换"