https://e2e.ti.com/support/logic-group/logic/f/logic-forum/892348/sn74lvc1g373-logic-forum

器件型号:SN74LVC1G373主题中讨论的其他器件: SN74LVC1G14、 SN74LS279A、 SN74LVC2G132

您好!

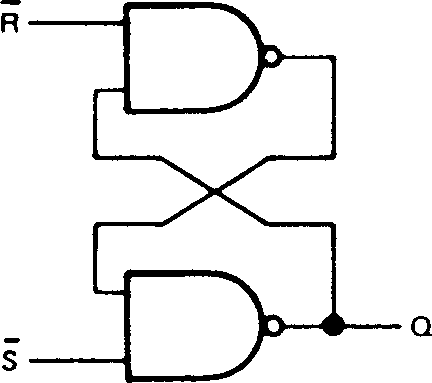

我的客户考虑以下电路。

在该电路上、上电后、该输出是否为以下逻辑波形? 请告诉我。

他希望:

当 D 引脚的输入在加电后变为高电平、此 SN74LVC1G373在 Q 引脚上输出高电平至低电平、并保持低电平。

如果您有任何替代解决方案、请告知我们。

谢谢、此致、

M.Hattori。