Other Parts Discussed in Thread: SN74AVCH16T245, ADS8568

https://e2e.ti.com/support/logic-group/logic/f/logic-forum/939469/sn74avch16t245-notch-in-waveform

器件型号:SN74AVCH16T245主题中讨论的其他器件: ADS8568

大家好、我的项目使用 SN74AVCH16T245来连接 ADS8568 (3.3V)和 C6657 (1.8V)之间的并行端口。 C6657使用 EMIF 驱动和读取 ADS8568。

但读取的结果具有一些错误数据。 我测量了 EMIF 总线的波形。

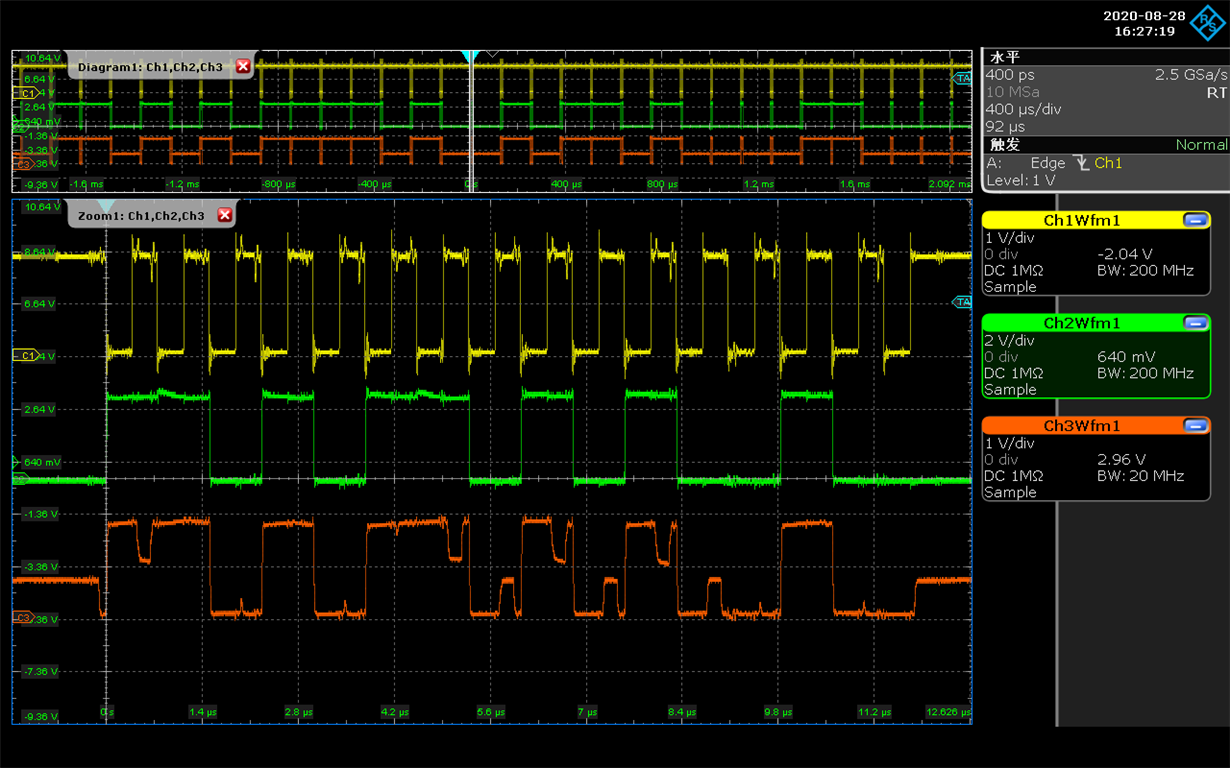

波形如下所示。 黄色波为 OE、绿色波为 ADS8568侧的 EMIF_D[x]、橙色波为 C6657侧的 EMIF_D[x]。

您可以在橙色波形中看到一些"陷波"。

我想这就是原因、但我不知道这是如何发生的。

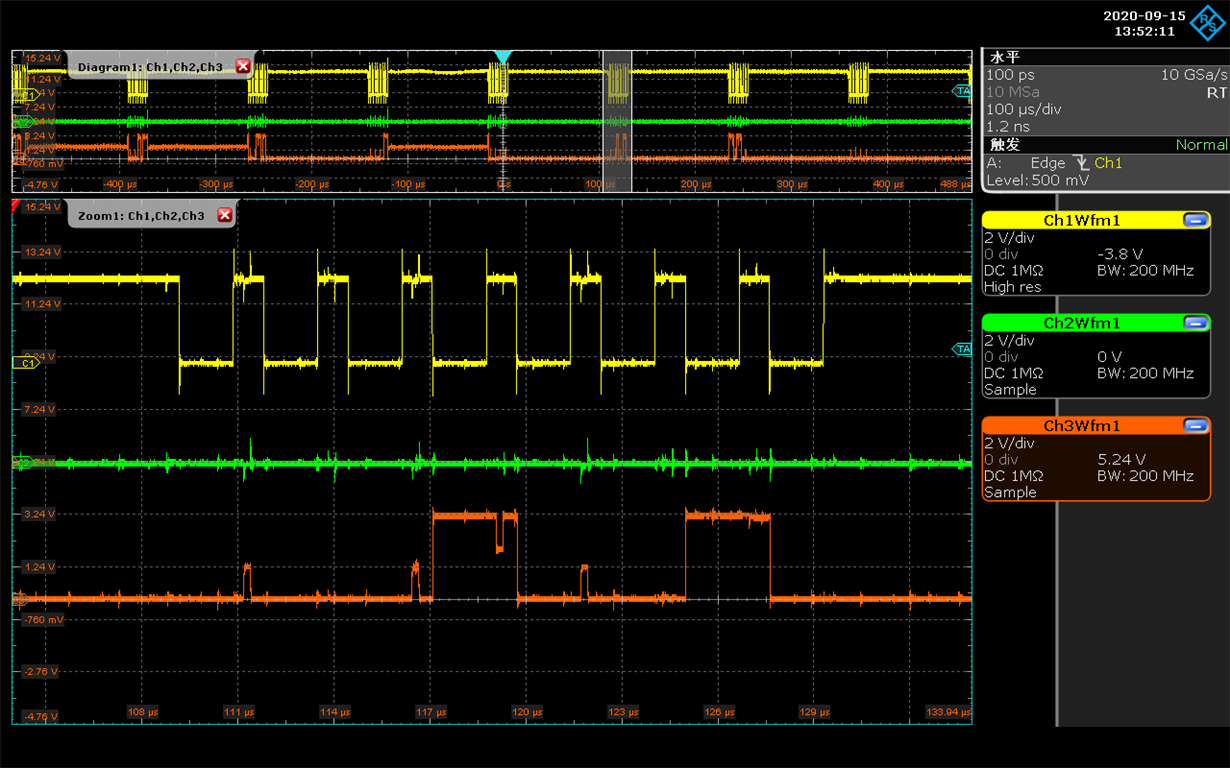

我还将 C6657 (1.8V)更改为 C6748 (3.3V)、但结果与下面的结果相同。 黄色波是 OE、橙色波是 C6748侧的 EMIF_D[x]。

如果电压收发器的 DSP 侧保持悬空、即电压收发器连接 ADS8568、但不连接 DSP 的 EMIF_D[x]端口、则波形和 ADS8568侧也会变得正常。

因此、我想知道它是如何发生的以及如何解决的。 谢谢!