请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

常见问题解答:逻辑和电压转换 > 输出参数>>电流常见问题解答

****请务必注意,此常见问题解答涉及 CMOS 器件。 双极器件不应以这种方式并联。 ****

将输出连接在一起的主要问题被称为"总线争用"。

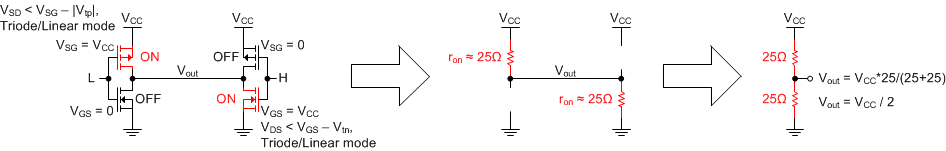

如果一个输出驱动为高电平、另一个输出驱动为低电平、则表示存在总线争用、并且器件可能会损坏。 下面是一个典型 LVTTL 驱动器的示例:

在上图中、一个 CMOS 输出表示为一对 NMOS 和 PMOS 晶体管。 这是 CMOS 输出的一种非常典型的布置。

如果我们为 Vcc 使用5V 电源、则很容易计算出预期电流、因为 Iout = 5/(25+25)= 100mA。 对于大多数逻辑 CMOS 输出、此电流超过数据表的绝对最大值、并且有可能损坏器件。

可以将器件的通道并联以增加驱动强度-确保两个输出始终处于相同状态非常重要。 实现这一目标的最佳方法是在同一器件中使用两个通道、并将输入直接连接在一起以确保它们始终具有相同的状态。