大家好、

客户使用 SN74LV123A 驱动具有100 Ω 串联电阻的光耦合器的 LED。

SPICE 仿真显示、输出下降(1Q)至~1.5V、消耗的电流为2.7mA、Vdd 为3.3V、LED 下降的电压为~ 1.4V。 这似乎使得1.4V + 100*2.7mA 为~ 1.7V、从而在 SN74LV123A (1Q)的输出上留下了3.3V-1.7V 的电压。

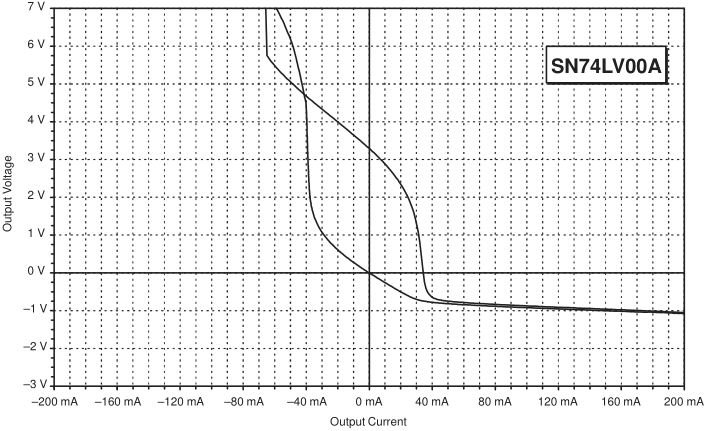

数据表中没有提到输出电压与电流的关系。

- 仿真模型是否正确? 如果以所述方式加载器件输出、输出电压是否会降至1.5V?

- 是否可以从器件中消耗这么大的电流? 部件是否会长期损坏。

谢谢、

此致、

Joe