主题中讨论的其他器件: SN74LVC1G08、 SN74LVC14A

这是我的 CD40109B 电路、其中 R26.1 = 4x10K、R25.1-A = 4x100K 、CX.1-.4 = 47pF:

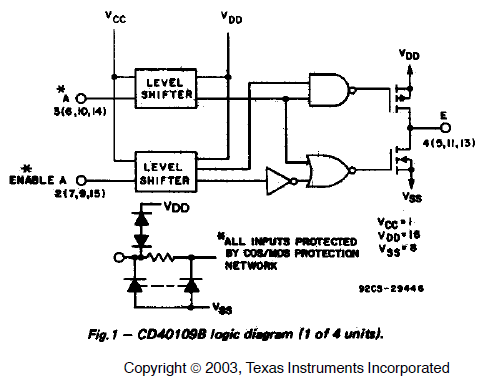

为了防止输入上升到高于 Vcc 输入、假设 通过 R26电阻器的电流不超过最大输入电流、下面图1底部所示的输入保护二极管电路就足够了。

但是、我有一些不确定因素...

a)我假设/期望数据表中每个引脚额定值的最大输入电流

是 数据表底部图1所示输入保护电路的额定值 (因为图中显示“*所有受 COS/MOS 保护网络保护的输入”)。 但是、该图显示了连接到 VDD 而不是 VCC 的二极管的顶部。 这是一个错误,还是我误解了这个图的功能/目的(或者两者都是真的)。

例如、如果 VCC 的值小于 VDD、并且这些输入被钳位到 VDD、那么根据 VDD、输入的范围似乎是有限的(根据 IC 的电平转换功能、这对我来说是没有意义的)。

b)同样、在图1中、二极管的顶部显示两个连接阳极到阳极的二极管;我不理解这可以提供什么保护、除非我 假设这些仅在顶部二极管达到其反向电压额定值时提供保护。 如果没有、 该电路如何提供保护? 如果 是、它钳制的额定电压是多少?

c)是否已经有任何文档解释了这些详细信息?

d)数据表是一 份带有更改的旧影印件(我假设 TI 通过购买其他公司获得了此设计)。 TI 是否会随时创建更新的数据表?