我正在使用 CD4059AM 的应用中、在该应用中、JAM 输入1至7由 MCU 控制以提供不同的分频值。 多个输入可以一次改变、并且它们都应该相对即时地改变。 对于给定的输入、预计最短的导通或关断时间约为8ms、即最快变化的输入为8ms 导通、8ms 关断等

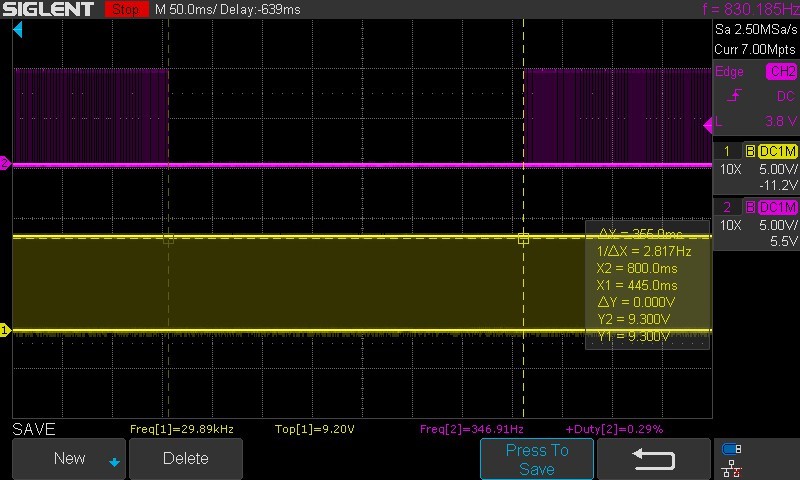

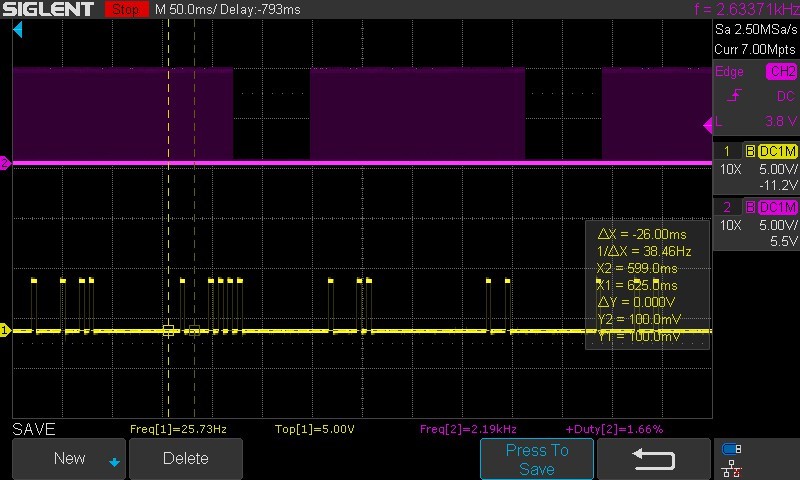

在大多数情况下、电路按预期工作、但我偶尔会遇到 GND 处的输出平线脉冲。 在此期间、输入仍处于活动状态、因此信号在经过 CD4059时会丢失。 从我看到的情况来看、突发持续时间从大约150ms 到600ms 不等。

我只能想象、如此快速地更改 JAM 输入会产生某种计数器不喜欢的状态。 这种理论得到以下事实的支持:如果我降低输入变化的速率、行为就会消失。 但是、我在数据表中看不到任何关于这种特定类型限制的内容。 因此、我想知道、首先、输入变化过快是否有意义、其次、如果这是一个限制因素、那么安全运行区域是什么? 是否有任何方法可以改进它?

顺便说一下、我几乎肯定的是、这与 MCU 程序无关、因为我还使用并行输出 ADC 构建了该项目的第一次迭代以控制 JAM 输入、我得到的问题完全相同。