Other Parts Discussed in Thread: SN74HC164

主题中讨论的其他器件:SN74HC164

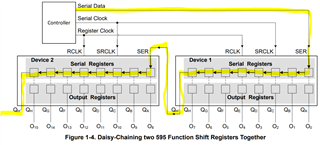

非常感谢论坛就有关54HC595 8位移位寄存器的先前问题提供意见。 我想问一个相关问题,该问题解决了当 QH 的输出从下一个移位寄存器馈入 SER 输入时,两个级联移位寄存器输出的脉冲的时序问题。

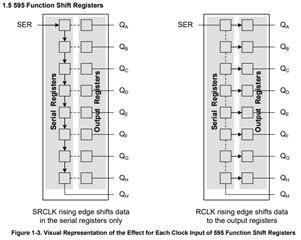

根据数据表中的时序图、输出 qb 比 Qa 晚1个时钟周期、输出 qc 比 qb 晚1个时钟周期、以此类推。 QH’是 QH 前半个时钟周期。 因此,如果我将 QH 馈入下一个移位寄存器的 SER 线,该脉冲将在后面的 Qa2处产生一个时钟脉冲。 因此、如果我从第一个移位寄存器将 Qa 与 QH 对齐、 第二个移位寄存器的 Qa2我认为第二个移位寄存器的 Qa2与第一个移位寄存器的 QH 不会有1个时钟周期的距离、因为它比第一个移位寄存器的最后一个输出的前半个时钟周期。 因此,如果我希望 54HC595的级联移位寄存器之间的数据之间有一个时钟周期的间隔,则应该将 QH 发送到下一个移位寄存器,或者可能使用 QH。 很抱歉、我之前没有占用这么多 TI 论坛带宽。 谢谢、Bob Wagner